5 dsp status register (dsr), Dsp status register (dsr) -35, Dsp status register (dsr) bit definitions -35 – Motorola DSP56301 User Manual

Page 153: 5 dsp status register (dsr)

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-35

6.7.5

DSP Status Register (DSR)

.

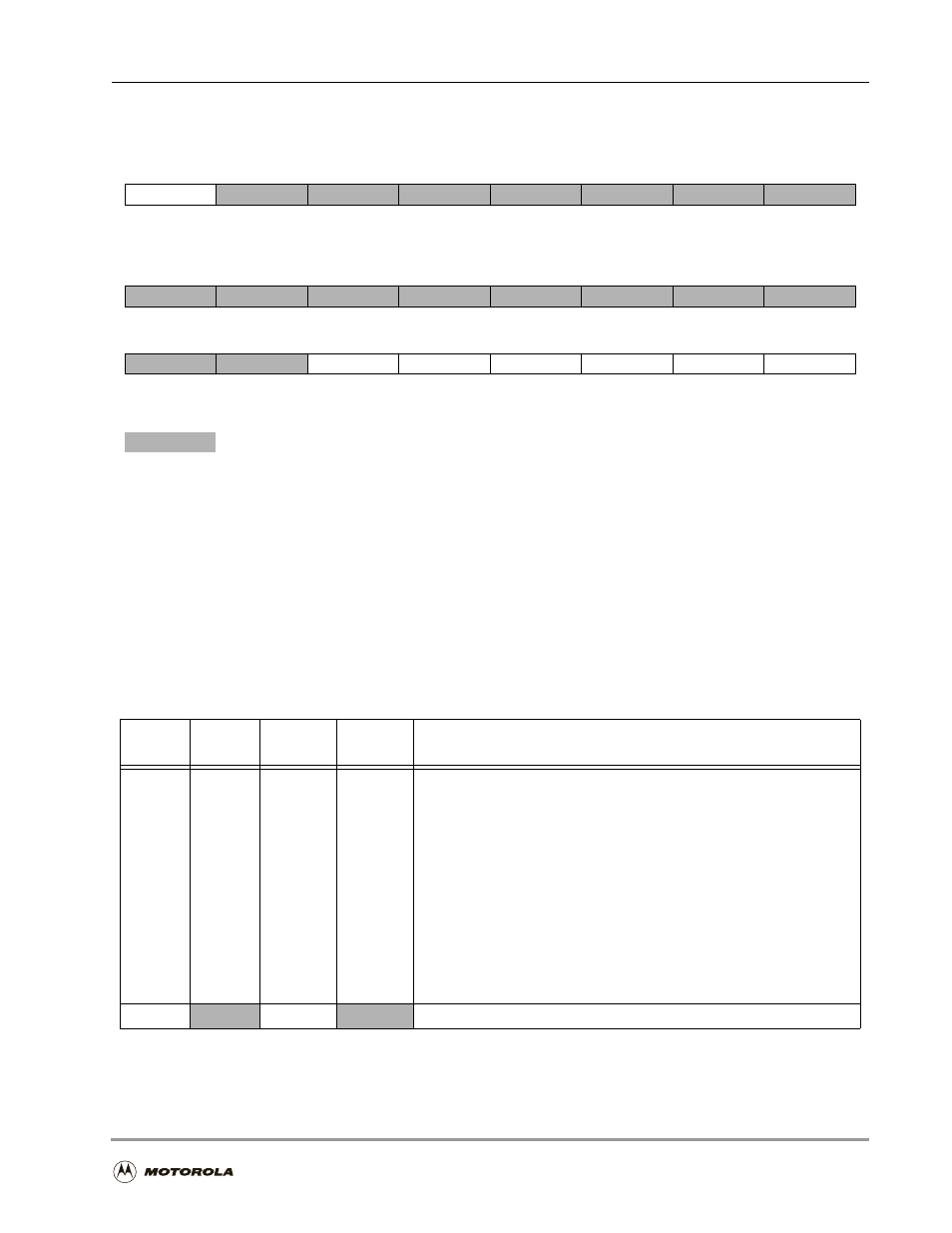

A 24-bit read-only status register by which the DSP56300 core examines the HI32 status and

flags. The host processor cannot access DSR.

Note:

When data is written to the HI32, there is a two-cycle pipeline delay while any

status bits affected by this operation are updated. If any of the status bits are read

during the two-cycle delay, the status bit may not reflect the current status.

23

22

21

20

19

18

17

16

HACT

UBM

PCI

SC

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

HF2

HF1

HF0

SRRQ

STRQ

HCP

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

UBM

PCI

Reserved. Write to 0 for future compatibility

UBM = Universal Bus mode

PCI = PCI mode

SC = Self-Configuration mode

Figure 6-9. DSP Status Register (DSR)

Table 6-14. DSP Status Register (DSR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Mode

Description

23 HACT

0

UBM

PCI

SC

HI32 Active

Indicates the activity of the HI32. HACT is set when DCTR[HM] = $1,

$2, $3, or $5. HACT is cleared in response to Terminate and Reset

(DCTR[HM] = $0):

n

While the HI32 is an active PCI bus master or selected target in a

memory space transaction, a master-initiated termination or

target disconnect, respectively, is generated. When the PCI idle

state is detected, HACT is cleared.

n

While the HI32 is in a Universal Bus or Self-Configuration mode

(DCTR[HM] = $2, $3 or $5), the HACT status bit in the DSR is

cleared immediately.

When HACT is set, the HI32 is active, and the DCTR mode and polarity

bits must

not be changed.

22–6

0

Reserved. Write to 0 for future compatibility.