2 interrupt table memory map, Interrupt table memory map -17, Interrupt priority level bits -17 – Motorola DSP56301 User Manual

Page 91: Interrupt sources -17

Configuring Interrupts

Core Configuration

4

-17

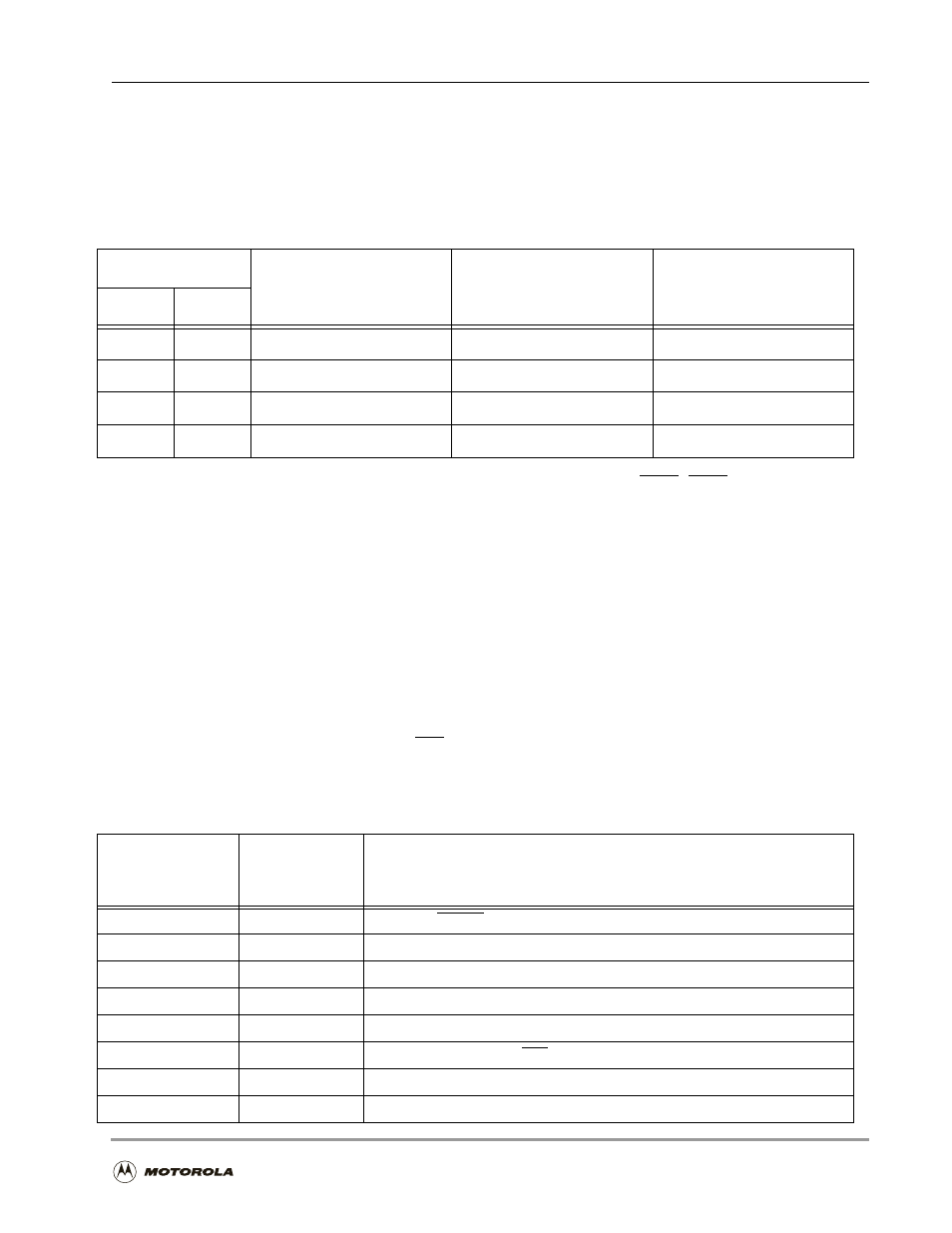

The DSP56301 has a four-level interrupt priority structure. Each interrupt has two

interrupt priority level bits (IPL[1–0]) that determine its interrupt priority level. Level 0 is

the lowest priority; Level 3 is the highest-level priority and is non-maskable. Table 4-5

defines the IPL bits.

The IPRC also selects the trigger mode of the external interrupts (

IRQA

–

IRQD

). If the value

of the IxL2 bit is 0, the interrupt mode is level-triggered. If the value is 1, the interrupt

mode is negative-edge-triggered.

4.4.2

Interrupt Table Memory Map

Each interrupt is allocated two instructions in the interrupt table, resulting in 128 table

entries for interrupt handling. Table 4-6 shows the table entry address for each interrupt

source. The DSP56301 initialization program loads the table entry for each interrupt

serviced with two interrupt servicing instructions. In the DSP56301, only some of the 128

vector addresses are used for specific interrupt sources. The remaining interrupt vectors

are reserved and can be used for host

NMI

(IPL = 3) or for host command interrupt

(IPL = 2). Unused interrupt vector locations can be used for program or data storage.

Table 4-5. Interrupt Priority Level Bits

IPL bits

Interrupts Enabled

Interrupts Masked

Interrupt Priority Level

xxL1

xxL0

0

0

No

—

0

0

1

Yes

0

1

1

0

Yes

0, 1

2

1

1

Yes

0, 1, 2

3

Table 4-6. Interrupt Sources

Interrupt

Starting Address

Interrupt

Priority Level

Range

Interrupt Source

VBA:$00

3

Hardware RESET

VBA:$02

3

Stack error

VBA:$04

3

Illegal instruction

VBA:$06

3

Debug request interrupt

VBA:$08

3

Trap

VBA:$0A

3

Nonmaskable interrupt (NMI)

VBA:$0C

3

Reserved

VBA:$0E

3

Reserved