Motorola DSP56301 User Manual

Page 171

Host-Side Programming Model

Host Interface (HI32)

6

-53

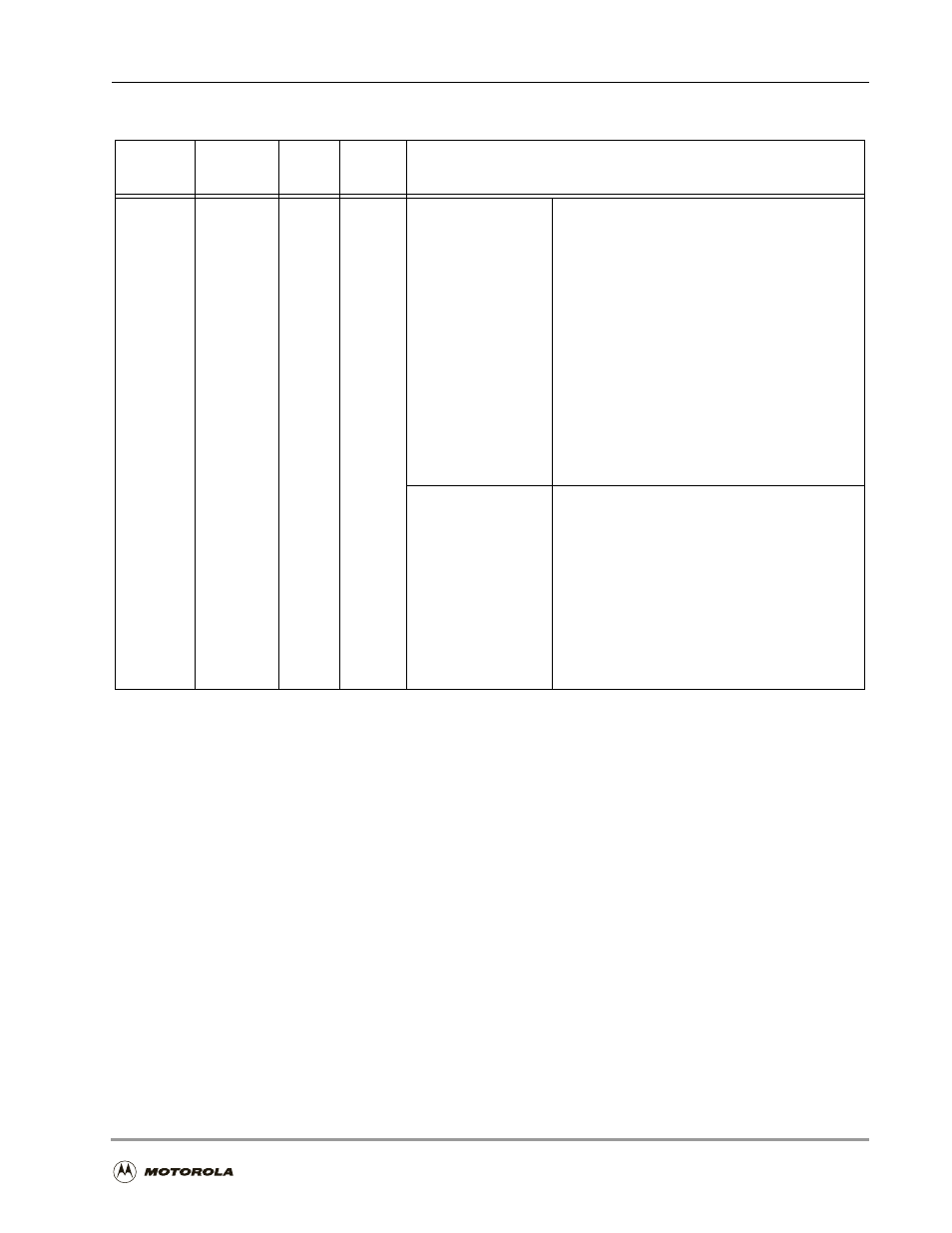

7 Cont.

SFT Cont.

0

UBM

PCI

Universal Bus mode

(DCTR[HM]

=

$2 or

$3)

Fetch (SFT = 1):

There is no FIFO buffering of the DSP-to-host

data path. Writing SFT = 1 resets the DSP-to-host

data path and clears the STRQ and the

HSTR[HRRQ]. At the beginning of a read data

transfer from the HRXS, STRQ is set. STRQ is

cleared when the DSP56300 core writes to the

DTXS; HSTR[HRRQ] is cleared if the HRXS is

empty and set if it contains data to be read by an

external host. If the host is not reading from the

HRXS, the DSP-to-host data path is forced to the

reset, and STRQ and HSTR[HRRQ] are cleared.

Note:

Any data remaining in the DSP-to-host

data path is lost when the reset state is

entered.

PCI and Universal Bus

modes (DCTR[HM]

=

$1, $2 or $3)

Pre-fetch (SFT = 0):

The DSP-to-host data path is a six word deep

FIFO buffer (three words deep in the 32-bit data

format mode, DCTR[HM] = $1 and HCTR[HRF] =

$0). STRQ reflects the status of the DTXS, and

HSTR[HRRQ] reflects the status of the HRXS.

STRQ is set if the DTXS is not full and cleared

when the DSP56300 core fills the DTXS.

HSTR[HRRQ] is cleared if the HRXS is empty,

and set when it contains data to be read by an

external host.

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description