4 sci initialization, Sci initialization -6, 4 sci initialization – Motorola DSP56301 User Manual

Page 242

SCI Initialization

8

-6

DSP56301 User’s Manual

8.4

SCI Initialization

The SCI is initialized as follows:

1.

Ensure that the SCI is in its individual reset state (PCRE = $0). Use a hardware

RESET

signal or software RESET instruction.

2.

Program the SCI control registers.

3.

Configure at least one SCI signal as an SCI signal.

If interrupts are to be used, the signals must be selected, and global interrupts must be enabled

and unmasked before the SCI can operate. The order does not matter; any one of these three

requirements for interrupts can enable the SCI, but the interrupts should be unmasked last

(that is, I[1–0] bits in the Status Register (SR) should be changed last). Synchronous

applications usually require exact frequencies, so the crystal frequency must be chosen

carefully. An alternative to selecting the system clock to accommodate the SCI requirements

is to provide an external clock to the SCI. When the SCI is configured in Synchronous mode,

internal clock, and all the SCI pins are simultaneously enabled, an extra pulse of one DSP

clock length is provided on the

SCLK

pin.

SSR

R8

FE

PE

OR

IDLE

RDRF

TDRE

TRNE

7

6

5

4

3

2

1

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

1

1

0

0

0

0

0

0

1

1

0

0

0

0

0

0

1

1

TCM

15

0

0

—

—

RCM

14

0

0

—

—

SCCR

SCP

13

0

0

—

—

COD

12

0

0

—

—

CD[11–0]

11–0

0

0

—

—

SRX

SRX[23–0]

23–16, 15–8, 7–0

—

—

—

—

STX

STX[23–0]

23–0

—

—

—

—

SRSH

SRS[8–0]

8–0

—

—

—

—

STSH

STS[8–0]

8–0

—

—

—

–

SRSH

SCI receive shift register, STSH—SCI transmit shift register

HW

Hardware reset is caused by asserting the external RESET signal.

SW

Software reset is caused by executing the RESET instruction.

IR

Individual reset is caused by clearing PCRE (bits 0–2) (configured for GPIO).

ST

Stop reset is caused by executing the STOP instruction.

1

The bit is set during this reset.

0

The bit is cleared during this reset.

—

The bit is not changed during this reset.

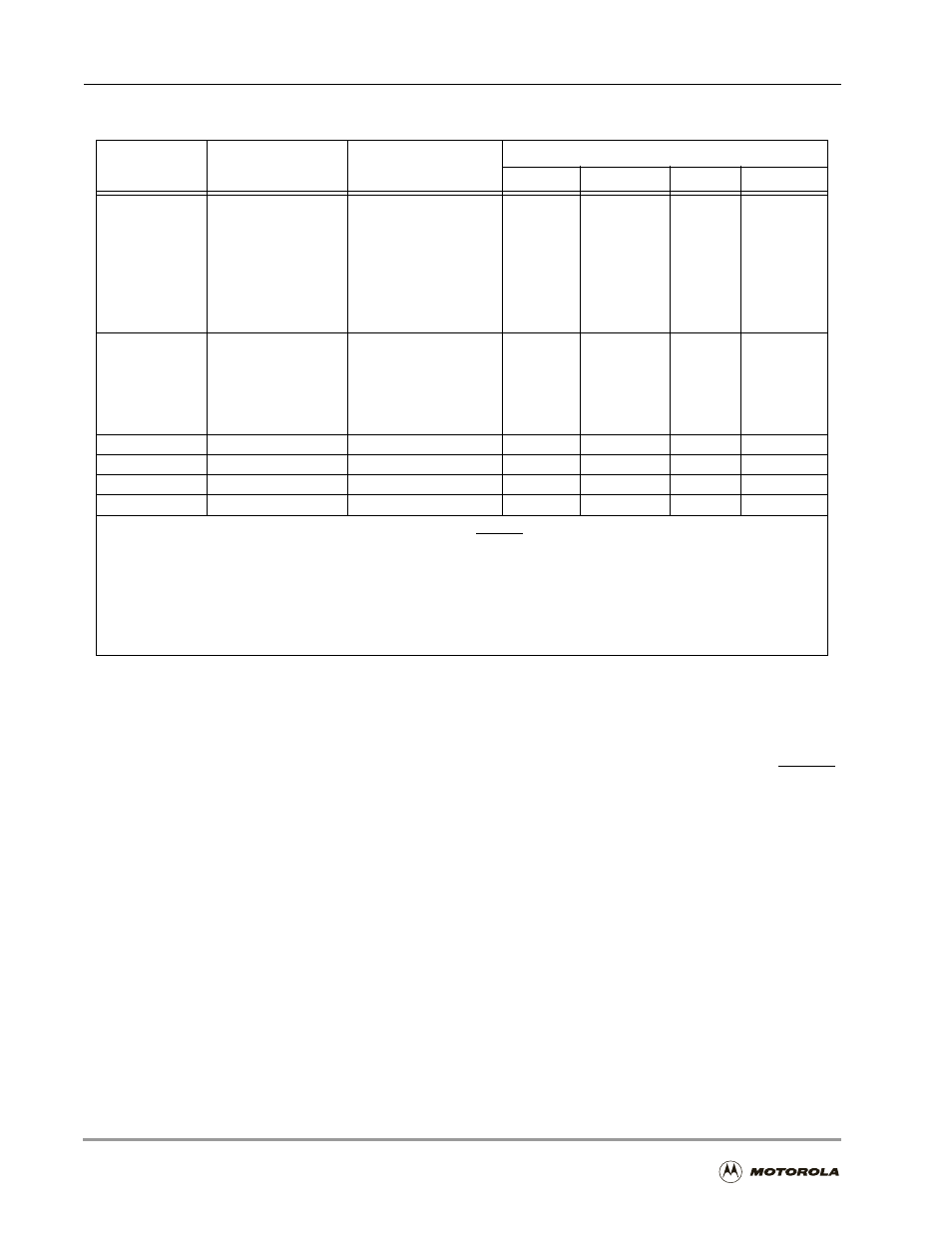

Table 8-1. SCI Registers After Reset (Continued)

Register

Bit Mnemonic

Bit Number

Reset Type

HW Reset

SW Reset

IR Reset

ST Reset