B-10, Figure b-10, Dsp control register (dctr) – Motorola DSP56301 User Manual

Page 334: Host processor (hi32), Figure b-10. dsp control register (dctr)

Programming Sheets

B

-22

DSP56301 User’s Manual

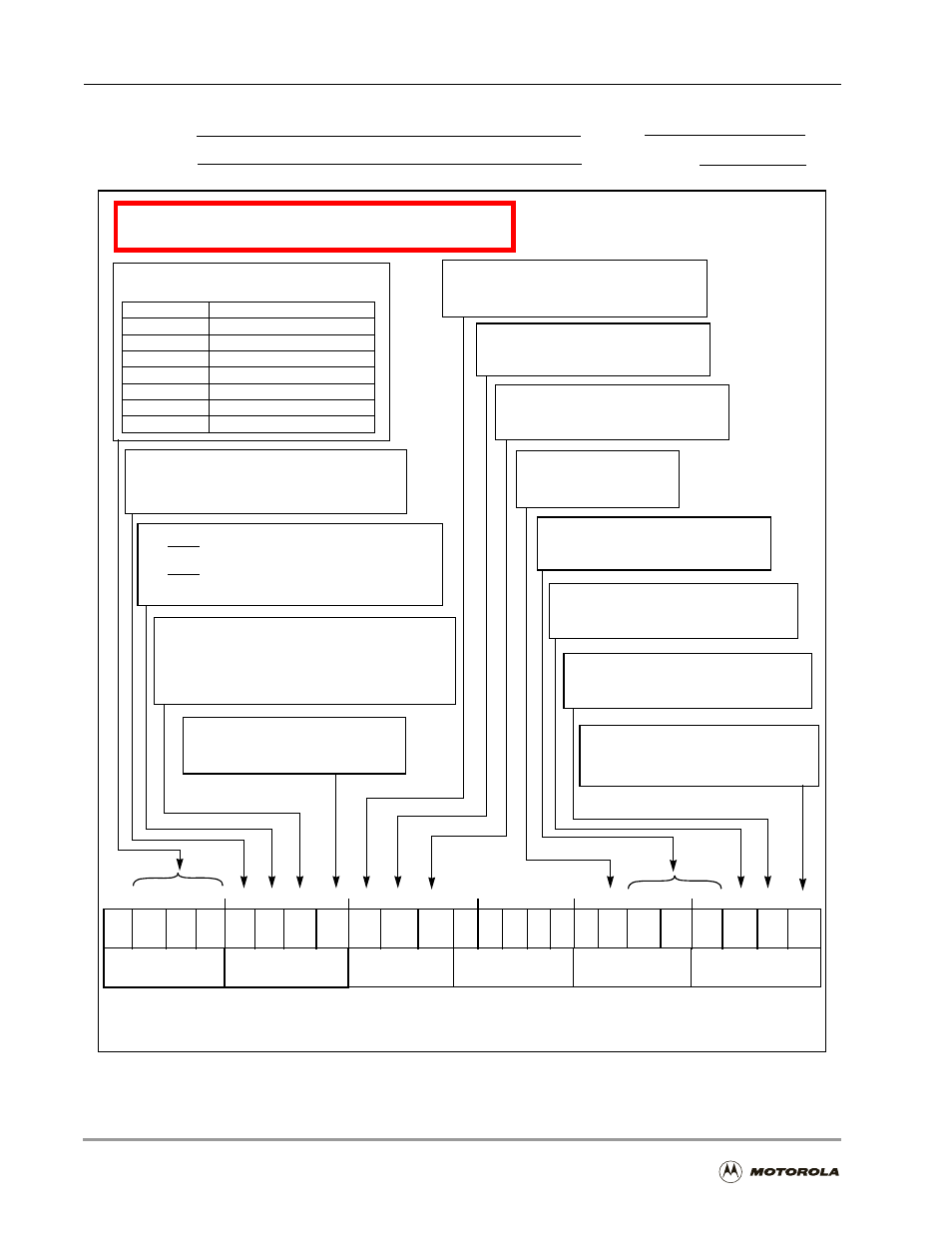

Figure B-10. DSP Control Register (DCTR)

Host Processor (HI32)

DSP Control Register (DCTR)

Reset = $000000

15 14

13

12 11 10 9

8

7

6

5

4

3

2

1

0

HF5

SRIE

STIE

19 18

17

16

23 22

21 20

HRWP HDSM

0 = Double-Strobe pin mode is selected

1 = Single-strobe pin mode is selected

HIRD HIRH

HM0

HM1

HM2

Host Command Interrupt Enable, Bit 0

Host Data Strobe Mode, Bit 13

Host Interrupt Request Drive Control, Bit 19

0 = HIRQ pin is an open-drain output

HI32 Mode

, Bits 22–20

HF4

HF3

0 = HINTA pin released

1 = HINTA pin driven low

Host Interrupt A, Bit 6

Used for DSP-to-host communication

Set or cleared by DSP, visible to host

Host Flags, Bits 5–3

Slave Transmit Interrupt Enable, Bit 1

1 = Core interrupt when DSR[STRQ] is set

0 = STRQ interrupt requests are disabled

1 = HIRQ pin is always driven

HINT

*

= Reserved, Program as 0

*

0

000

Terminate and Reset

001

PCI

010

Universal Bus

011

Enhanced Universal Bus

100

GPIO

101

Self-Configuration

110

Reserved

111

Reserved

Control HI32 operating modes, as follows:

*

0

*

0

*

0

*

0

*

0

*

0

HCIE

HRSP HDRPHRWP

Host Interrupt Request Handshake Mode, Bit 18

0 = HIRQ is asserted for specified number of core

1 = HIRQ is deasserted when interrupt request

Host Reset Polarity, Bit 17

0 = HRST pin is active high and the HI32 is reset

1 = HRST pin is active low and the HI32 is reset

clock cycles, which is set in the CLAT[LT]

source is cleared

if the HRST pin is high

if the HRST pin is low

1 = Core interrupt when DSR[HCP] is set

0 = HCP interrupt requests are disabled

Slave Receive Interrupt Enable, Bit 2

0 = SRRQ interrupt requests are disabled

0 = Host-to-DSP direction is low HRW

1 = Host-to-DSP direction is high HRW

Host Read/Write Polarity, Bit 14

0 = HDRQ pin is active high

1 = HDRQ pin is active low

Host DMA Request Polarity, Bit 16

0 = HTA is active high

1 = HTA is active low

Host Transfer Acknowledge Polarity, Bit 15

1 = Core interrupt when DSR[SRRQ] is set

Note: All bits but the mode setting bits (Bits 22–20) work only in a Universal Bus Mode (DCTR[HM] = $2 or $3)

Read/Write Address: X: FFFFC5

Application:

Date:

Programmer:

Sheet 1 of 10