B.1 internal i/o memory map – Motorola DSP56301 User Manual

Page 315

Internal I/O Memory Map

Programming Reference

B

-3

B.1

Internal I/O Memory Map

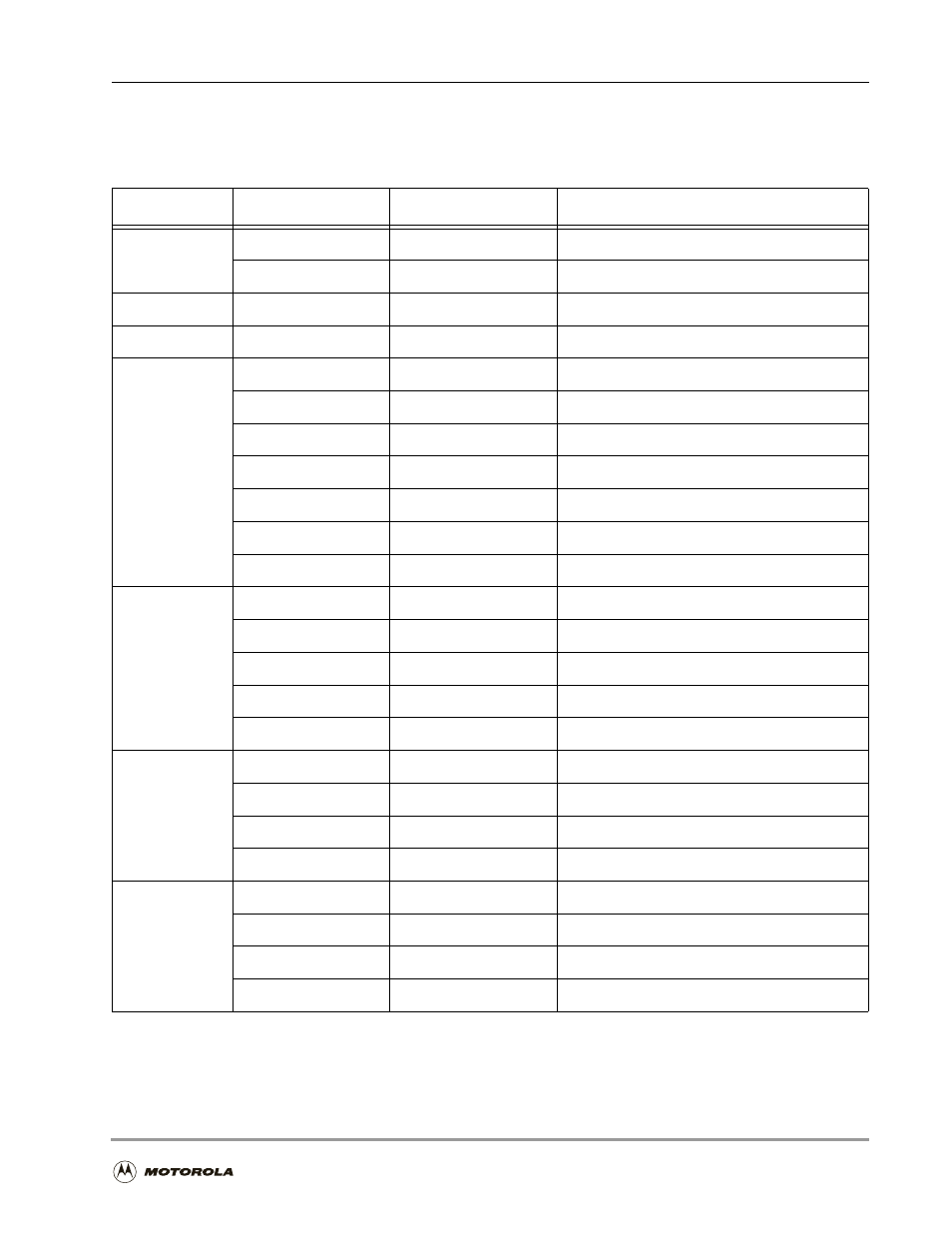

Table B-2. Internal I/O Memory Map (X Data Memory)

Peripheral

16-Bit Address

24-Bit Address

Register Name

IPR

$FFFF

$FFFFFF

Interrupt Priority Register Core (IPR-C)

$FFFE

$FFFFFE

Interrupt Priority Register Peripheral (IPR-P)

PLL

$FFFD

$FFFFFD

PLL Control Register (PCTL)

OnCE

$FFFC

$FFFFFC

OnCE GDB Register (OGDB)

BIU

$FFFB

$FFFFFB

Bus Control Register (BCR)

$FFFA

$FFFFFA

DRAM Control Register (DCR)

$FFF9

$FFFFF9

Address Attribute Register 0 (AAR0)

$FFF8

$FFFFF8

Address Attribute Register 1 (AAR1)

$FFF7

$FFFFF7

Address Attribute Register 2 (AAR2)

$FFF6

$FFFFF6

Address Attribute Register 3 (AAR3)

$FFF5

$FFFFF5

ID Register (IDR)

DMA

$FFF4

$FFFFF4

DMA Status Register (DSTR)

$FFF3

$FFFFF3

DMA Offset Register 0 (DOR0)

$FFF2

$FFFFF2

DMA Offset Register 1 (DOR1)

$FFF1

$FFFFF1

DMA Offset Register 2 (DOR2)

$FFF0

$FFFFF0

DMA Offset Register 3 (DOR3)

DMA0

$FFEF

$FFFFEF

DMA Source Address Register (DSR0)

$FFEE

$FFFFEE

DMA Destination Address Register (DDR0)

$FFED

$FFFFED

DMA Counter (DCO0)

$FFEC

$FFFFEC

DMA Control Register (DCR0)

DMA1

$FFEB

$FFFFEB

DMA Source Address Register (DSR1)

$FFEA

$FFFFEA

DMA Destination Address Register (DDR1)

$FFE9

$FFFFE9

DMA Counter (DCO1)

$FFE8

$FFFFE8

DMA Control Register (DCR1)