Motorola DSP56301 User Manual

Page 85

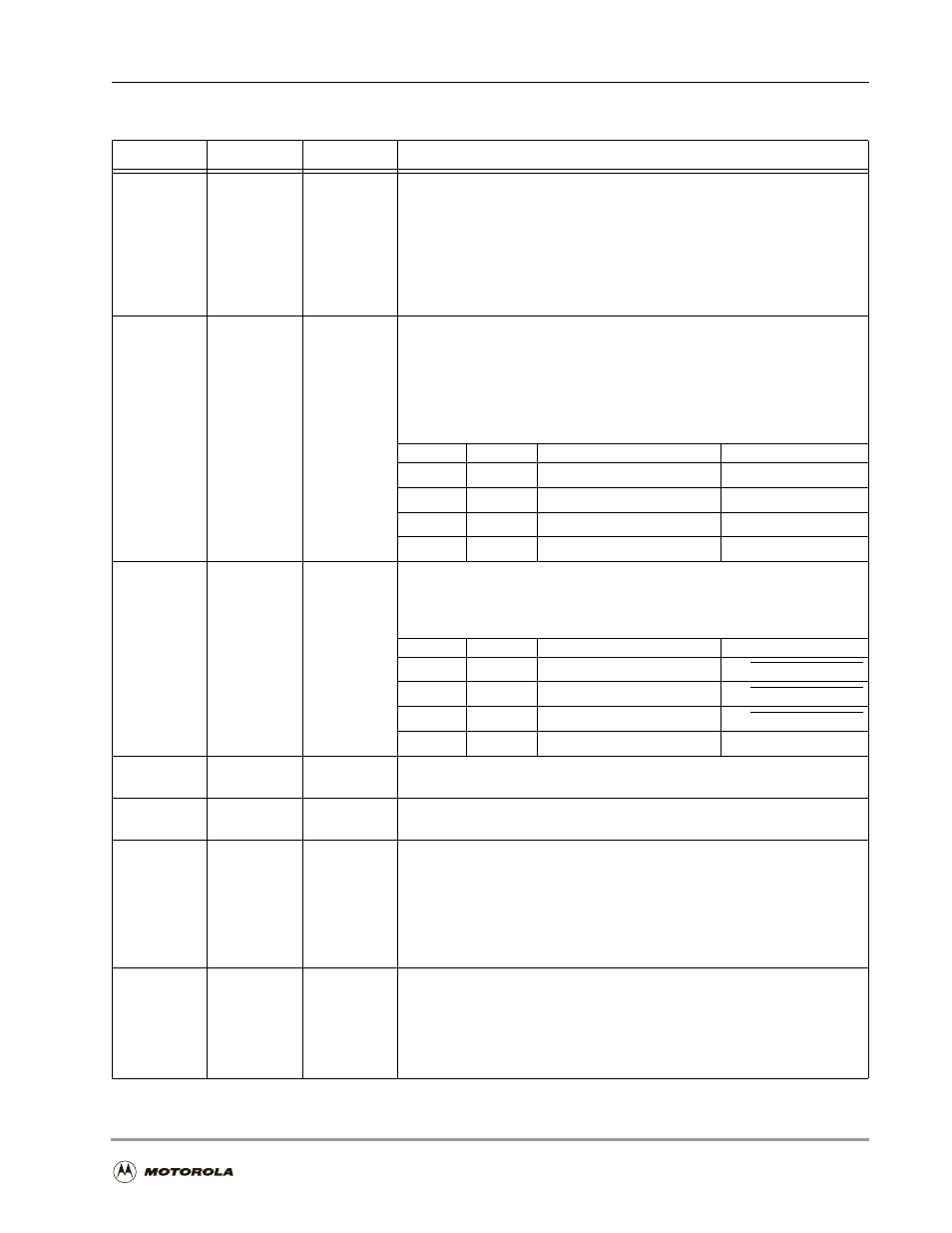

Central Processor Unit (CPU) Registers

Core Configuration

4

-11

6

L

0

Limit

Set if the overflow bit is set or if the data shifter/limiter circuits perform a

limiting operation. In Arithmetic Saturation mode, the L bit is also set when

an arithmetic saturation occurs in the Data ALU result; otherwise, it is not

affected. The L bit is cleared only by a processor reset or by an instruction

that specifically clears it (that is, a

sticky bit); this allows the L bit to be used

as a latching overflow bit. The L bit is affected by data movement

operations that read the A or B accumulator registers.

5

E

1

Extension

Cleared if all the bits of the integer portion of the 56-bit result are all ones or

all zeros; otherwise, this bit is set. The Scaling mode defines the integer

portion. If the E bit is cleared, then the low-order fraction portion contains all

the significant bits; the high-order integer portion is sign extension. In this

case, the accumulator extension register can be ignored. If the E bit is set, it

indicates that the accumulator extension register is in use.

S1

S0

Scaling Mode

Integer Portion

0

0

No scaling

Bits 55–47

0

1

Scale down

Bits 55–48

1

0

Scale up

Bits 5–46

1

1

Reserved

Undefined

4

U

0

Unnormalized

Set if the two MSBs of the Most Significant Portion (MSP) of the result are

identical; otherwise, this bit is cleared. The MSP portion of the A or B

accumulators is defined by the Scaling mode.

S1

S0

Scaling Mode

Integer Portion

0

0

No scaling

U = (Bit 47 XOR Bit 46)

0

1

Scale down

U = (Bit 48 XOR Bit 47)

1

0

Scale up

U = (Bit 46 XOR Bit 45)

1

1

Reserved

U undefined

3

N

0

Negative

Set if the MSB of the result is set; otherwise, this bit is cleared.

2

Z

0

Zero

Set if the result equals zero; otherwise, this bit is cleared.

1

V

0

Overflow

Set if an arithmetic overflow occurs in the 56-bit result; otherwise, this bit is

cleared. V indicates that the result cannot be represented in the

accumulator register (that is, the register overflowed). In Arithmetic

Saturation mode, an arithmetic overflow occurs if the Data ALU result is not

representable in the accumulator without the extension part (that is, 48-bit

accumulator or the 32-bit accumulator in Arithmetic Sixteen-bit mode).

0

C

0

Carry

Set if a carry is generated by the MSB resulting from an addition operation.

This bit is also set if a borrow is generated in a subtraction operation;

otherwise, this bit is cleared. The carry or borrow is generated from Bit 55 of

the result. The C bit is also affected by bit manipulation, rotate, and shift

instructions.

Table 4-3. Status Register Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description