3 dsp pci master control register (dpmc), Dsp pci master control register (dpmc) -30, 3 dsp pci master control register (dpmc) – Motorola DSP56301 User Manual

Page 148

HI32 DSP-Side Programming Model

6

-30

DSP56301 User’s Manual

6.7.3

DSP PCI Master Control Register (DPMC)

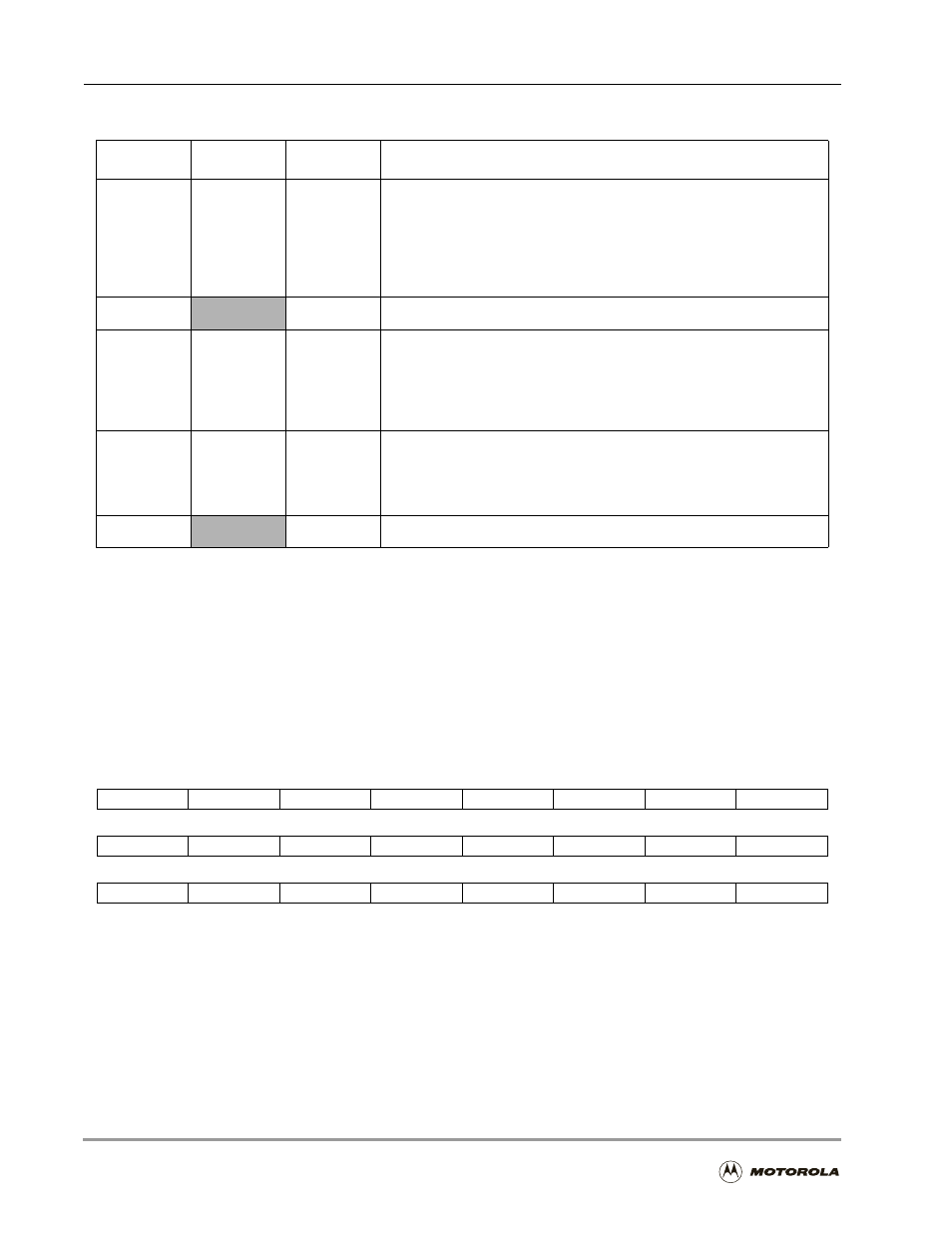

The DPMC is a 24-bit read/write register by which the DSP56300 core generates the two

most significant bytes of the 32-bit PCI transaction address and controls the burst length and

data transfer format. The host processor cannot access the DPMC. The DPMC bits are

ignored when the HI32 is not in PCI mode (DCTR[HM]

≠

$1). The DPMC can be written only

if MARQ is set or in Self-Configuration mode.

4

MAIE

0

Master Address Interrupt Enable

Enables/disables a DSP56300 core interrupt request when the HI32 is

not the PCI transaction initiator in the PCI mode (DCTR[HM]

=

$1). If

MAIE is cleared, master address interrupt requests are disabled. If

MAIE is set, a master address interrupt request is generated if the

master address request (MARQ) status bit in the DPSR is set.

3

0

Reserved. Write to 0 for future compatibility.

2

MRIE

0

Master Receive Interrupt Enable

Enables/disables a DSP56300 core interrupt request when the master

receive data request (MRRQ) status bit in the DSP Status Register

(DPSR) is set. If MRIE is cleared, master receive data interrupt

requests are disabled.

1

MTIE

o

Master Transmit Interrupt Enable

Enables/disables a DSP56300 core interrupt request when the master

transmit data request (MTRQ) status bit in the DPSR is set. If MTIE is

cleared, MTRQ interrupt requests are disabled.

0

0

Reserved. Write to 0 for future compatibility.

23

22

21

20

19

18

17

16

FC1

FC0

BL5

BL4

BL3

BL2

BL1

BL0

15

14

13

12

11

10

9

8

AR31

AR30

AR29

AR28

AR27

AR26

AR25

AR24

7

6

5

4

3

2

1

0

AR23

AR22

AR21

AR20

AR19

AR18

AR17

AR16

Figure 6-7. DSP PCI Master Control Register (DPMC)

Table 6-11. DSP PCI Control Register (DPCR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description