7 hi32 dsp-side programming model, Hi32 dsp-side programming model -22, Hi32 programming model, dsp side -22 – Motorola DSP56301 User Manual

Page 140: 7 hi32 dsp-side programming model

HI32 DSP-Side Programming Model

6

-22

DSP56301 User’s Manual

6.7

HI32 DSP-Side Programming Model

The DSP56300 core views the HI32 as a memory-mapped peripheral occupying eleven 24-bit

words in data memory space. Table 6-9 shows the HI32 DSP-side programming model.

The separate host-to-DSP and DSP-to-host data paths are FIFOs through which the HI32 and

the host processor transfer data efficiently and at high speeds. Memory mapping allows the

DSP56300 core to transfer data with the HI32 registers using standard instructions and

addressing modes. In addition, the MOVEP instruction allows HI32-to-memory and

memory-to-HI32 data transfers without the use of an intermediate register. The DSP56300

core can access the HI32 using either standard polling, interrupt, or DMA techniques. The

general-purpose DMA channels in the DSP56300 core can be programmed to transfer data

between the HI32 data FIFOs and other DMA accessible resources at maximum throughput

without DSP56300 core intervention. This section describes the purpose and operation of

each bit in the HI32 registers that are visible to the DSP56300 core. The HI32 host-side

programming model is described in Section 6.8, Host-Side Programming Model, on page

6-44.

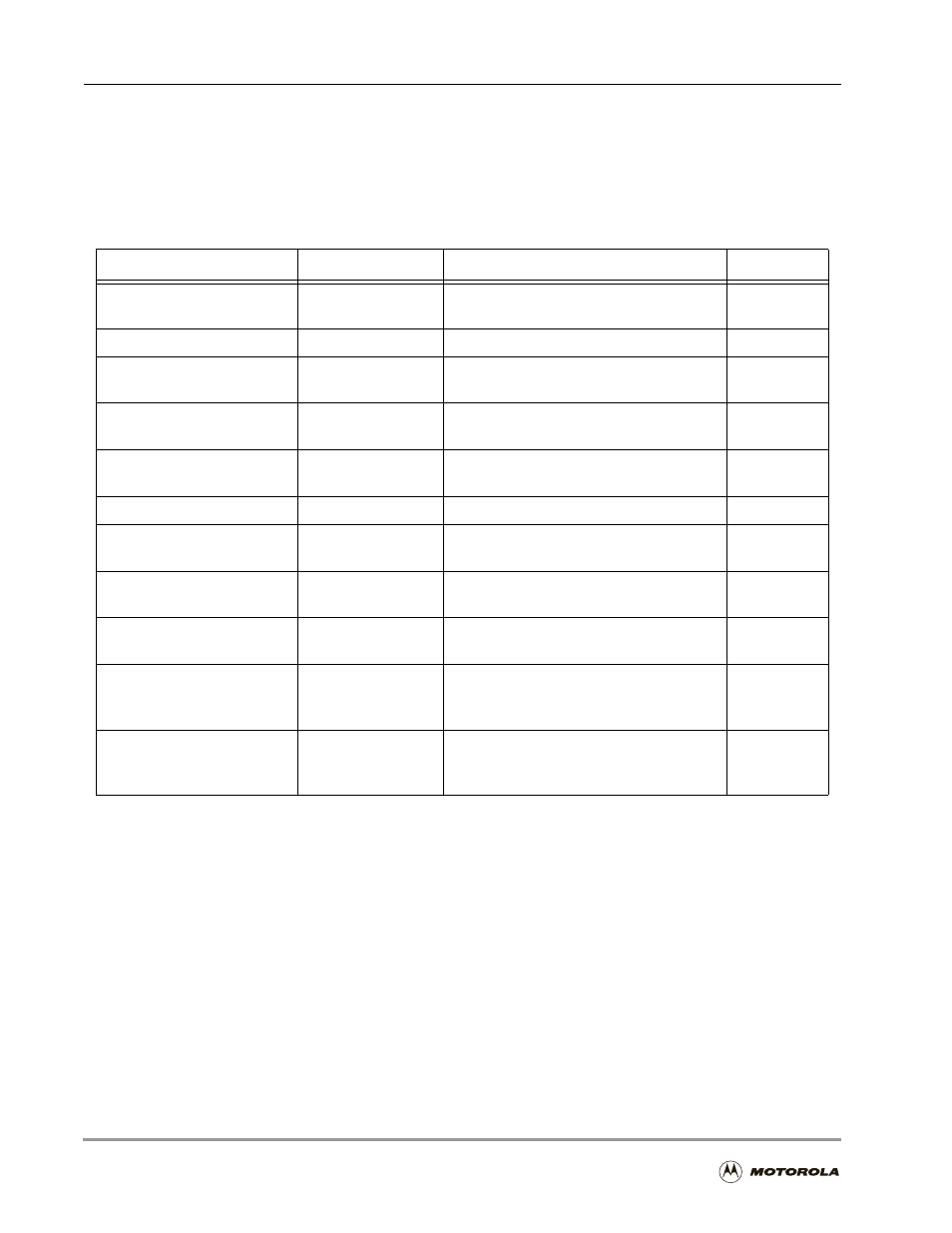

Table 6-9. HI32 Programming Model, DSP Side

X Memory Register Address

Mode

Register

Page

X:FFFFC5

PCI

Universal Bus

DSP Control Register (DCTR)

X:FFFFC6

PCI only

DSP PCI Control Register (DPCR)

X:FFFFC7

PCI

Self-Configuration

DSP PCI Master Control Register (DPMC)

X:FFFFC8

PCI

Self-Configuration

DSP PCI Address Register (DPAR)

X:FFFFC9

PCI

Universal Bus

DSP Status Register (DSR)

X:FFFFCA

PCI only

DSP PCI Status Register (DPSR)

X:FFFFCB

PCI

Universal Bus

DSP Receive Data FIFO (DRXR)

X:FFFFCC

PCI

Universal Bus

DSP Master Transmit Data FIFO (DTXM)

X:FFFFCD

PCI

Universal Bus

DSP Slave Transmit Data FIFO (DTXS)

X:FFFFCE

Universal Bus

(DCTR[HM] = $2)

GPIO

DSP Host Port GPIO Direction Register

(DIRH)

X:FFFFCF

Universal Bus

(DCTR[HM] = $2)

GPIO

DSP Host Port GPIO Data Register

(DATH)