Motorola DSP56301 User Manual

Page 149

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-31

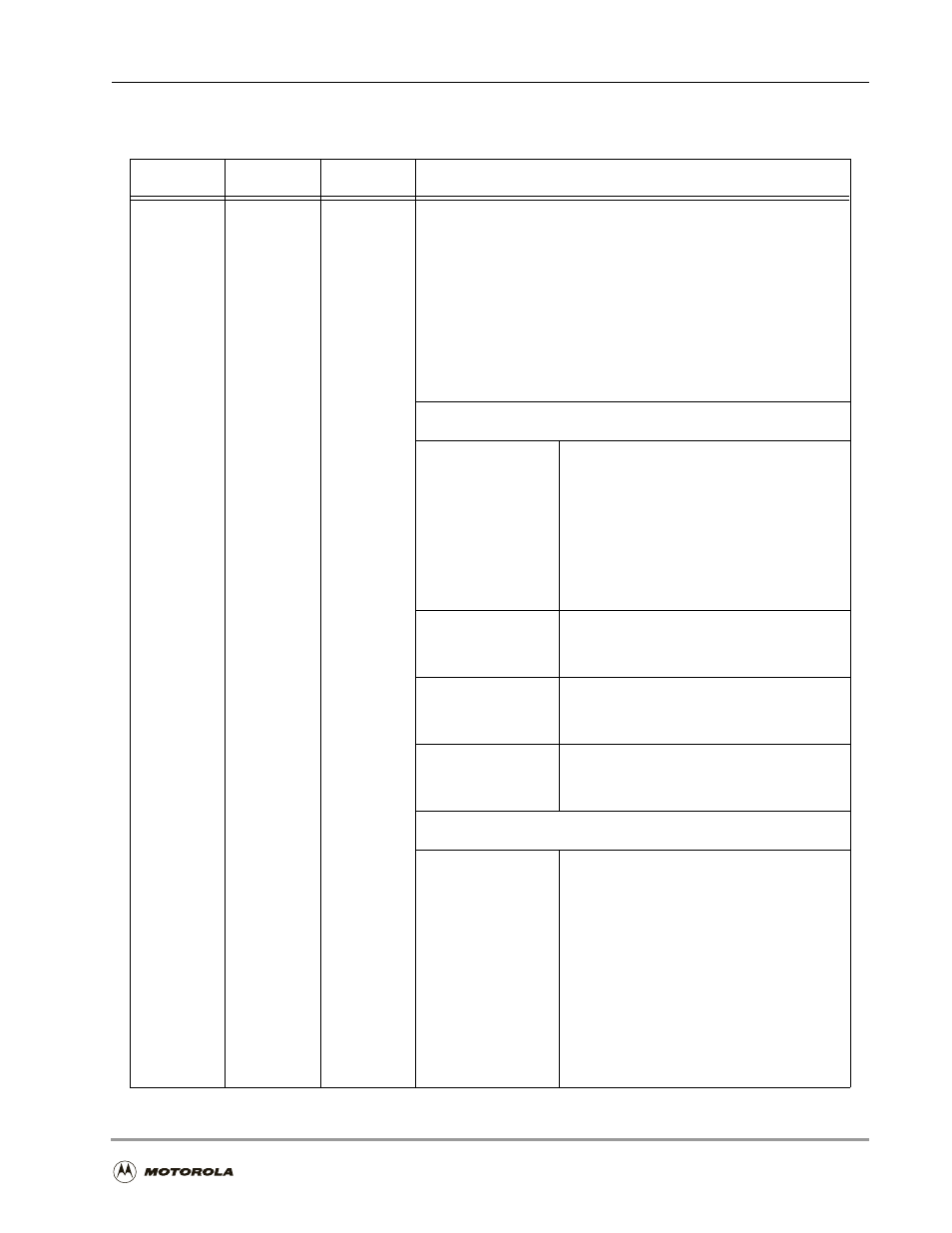

Table 6-12. DSP PCI Master Control Register (DMPC) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–22

FC[1–0]

0

Data Transfer Format Control

In PCI mode (DCTR[HM]

=

$1), define data transfer formats between

the HI32 and a PCI agent when the HI32 is a bus master. The data

transfer format converter) operates according to the specified

FC[1–0]. To assure proper operation: FC[1–0] can be changed only if

both the host-to-DSP and the DSP-to-host master data paths are

empty. In addition, switching between 32-bit data modes and

non-32-bit data modes may be done only in the personal software

reset state (DCTR[HM] = $0 and DSR[HACT] = 0). See Table 6-3 on

page 6-8 for a description of data transfer formats. FC[1–0] are

ignored when the HI32 is not in PCI mode (DCTR[HM]

≠

$1).

In a PCI DSP-to-Host transaction:

IFC = $0 (32-bit data

mode

The two least significant bytes of the first word

written to the DTXM and the two least

significant bytes of the second word written to

the DTXM are output to the HAD[31–0] pins.

HAD[31–0] = $HHHHLLLL, where LLLL are

the two least significant bytes of the first word

written to the DTXM and HHHH are the two

least significant bytes of the second word

written to the DTXM.

DPMC[FC] = $1

The data written to the DTXM is output to the

HAD[31–0] pins as right aligned and zero

extended in the most significant byte.

IFC = $2

The data written to the DTXM is output to the

HAD[31–0] pins as right aligned and sign

extended in the most significant byte.

DPMC[FC] = $3

The data written to the DTXM is output to the

HAD[31–0] pins as left aligned and zero filled

in the least significant byte.

In a PCI Host-to-DSP transaction:

DPMC[FC] = $0

(32-bit data mode)

The two least significant bytes PCI data bytes

from the HAD[15–0] pins are transferred to the

two least significant bytes of the DRXR after

which the two most significant bytes, from the

HAD[31–16] pins, are transferred to the two

least significant bytes of the DRXR. Thus,

when the DSP56300 core reads two words

from the DRXR, the two least significant bytes

of the first word read contain the two least

significant bytes of the 32-bit word written to

the HTXR, the two least significant bytes of

the second word read contain the two most

significant bytes of the 32-bit word.