Crb fsl0 and fsl1 bit operation (fsr = 0) -24 – Motorola DSP56301 User Manual

Page 222

ESSI Programming Model

7

-24

DSP56301 User’s Manual

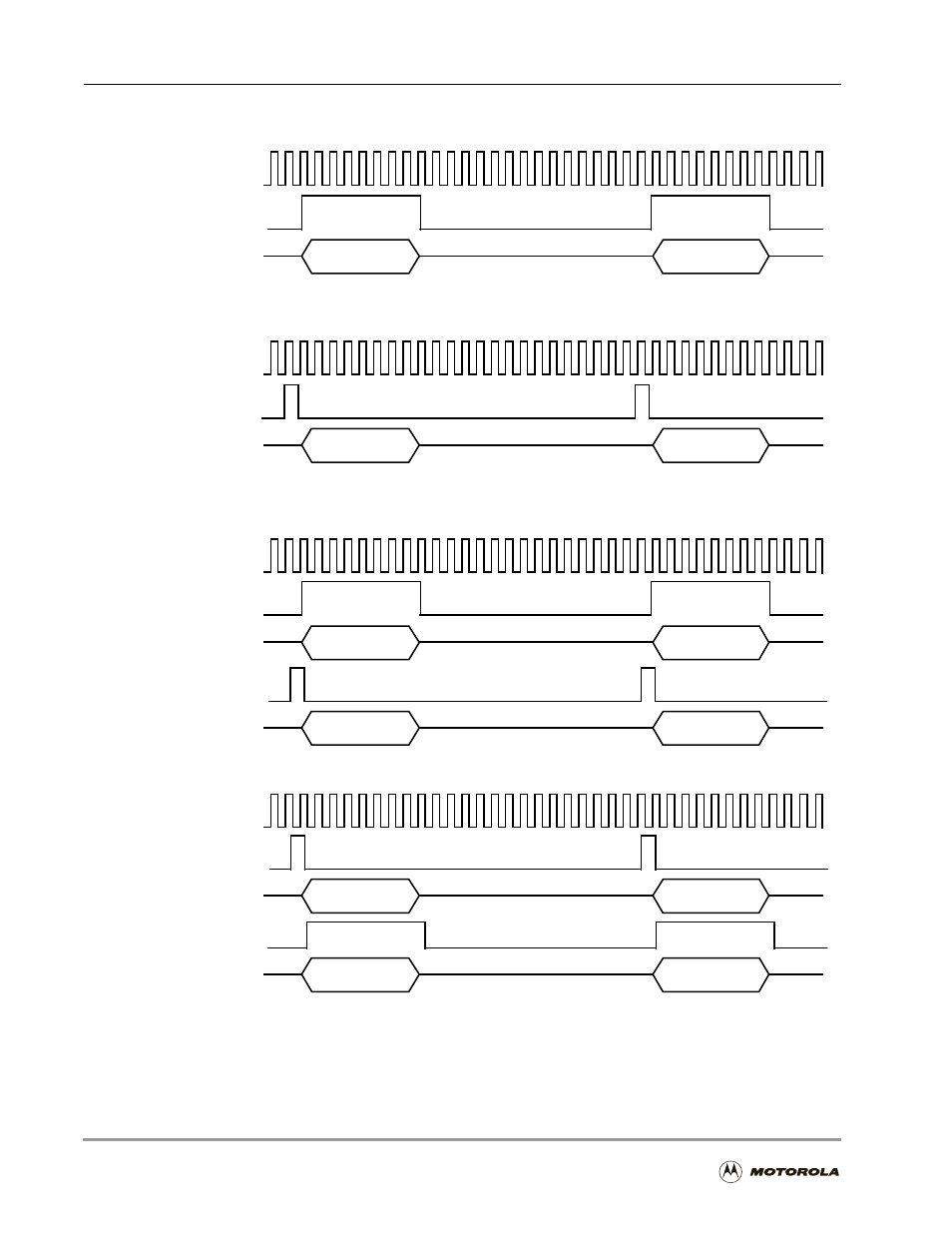

Figure 7-6. CRB FSL0 and FSL1 Bit Operation (FSR = 0)

Serial Clock

RX, TX Frame SYNC

Word Length: FSL1 = 0, FSL0 = 0

RX, TX Serial Data

Note:

Frame sync occurs while data is valid.

Data

Data

Serial Clock

RX, TX Frame SYNC

One Bit Length: FSL1 = 1, FSL0 = 0

RX, TX Serial Data

Note:

Frame sync occurs for one bit time preceding the data.

Serial Clock

TX Frame SYNC

Mixed Frame Length: FSL1 = 0, FSL0 = 1

RX Frame Sync

Serial Clock

TX Frame SYNC

Mixed Frame Length: FSL1 = 1, FSL0 = 1

TX Serial Data

RX Frame SYNC

Data

Data

Data

Data

Data

Data

Data

Data

Data

Data

RXSerial Data

TX Serial Data

RX Serial Data