Motorola DSP56301 User Manual

Page 291

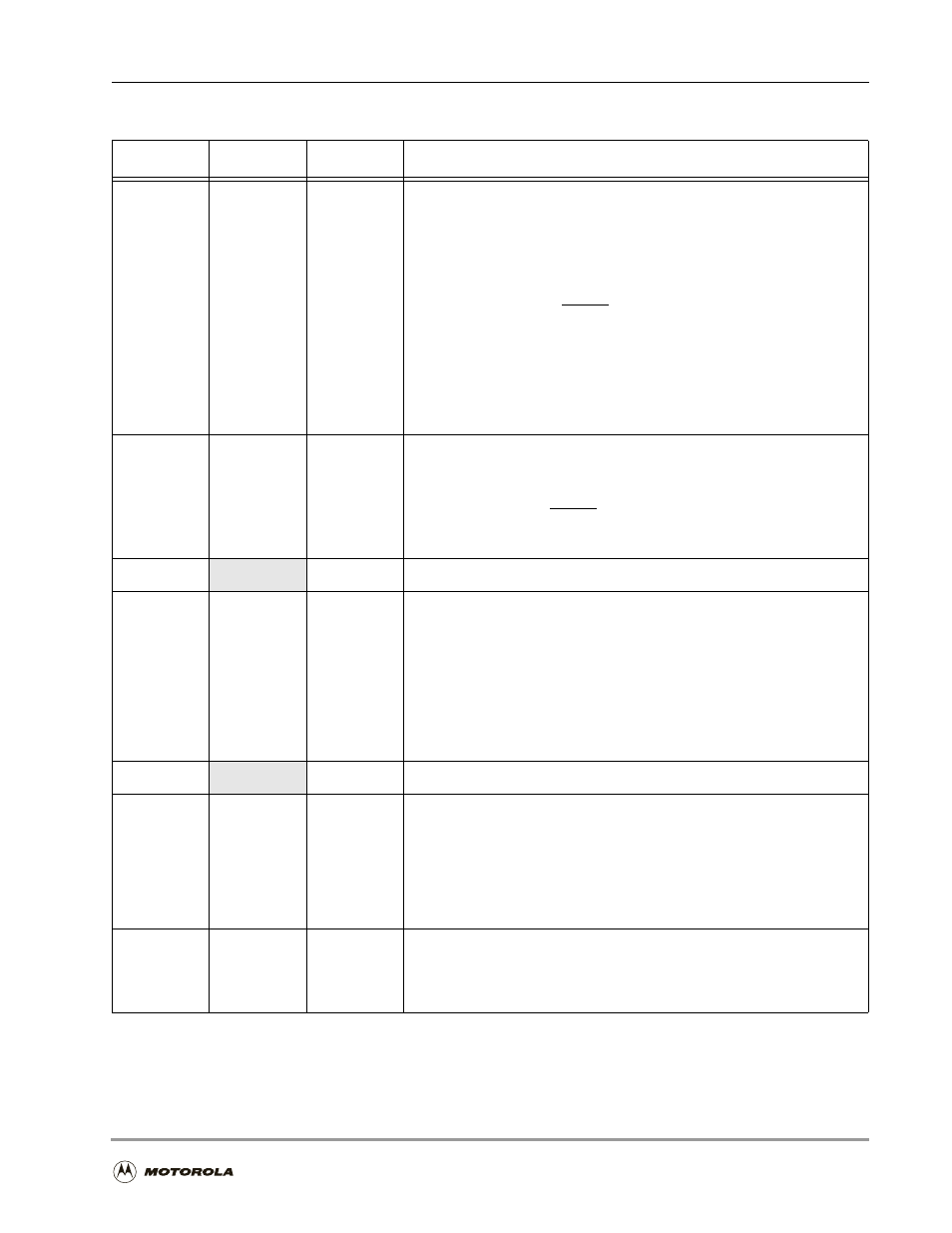

Triple Timer Module Programming Model

Triple Timer Module

9

-29

21

TCF

0

Timer Compare Flag

Indicate that the event count is complete. In timer, PWM, and watchdog

modes, the TCF bit is set after (M – N + 1) events are counted. (M is the

value in the compare register and N is the TLR value.) In measurement

modes, the TCF bit is set when the measurement completes. Writing a one

to the TCF bit clears it. A zero written to the TCF bit has no effect. The bit

is also cleared when the timer compare interrupt is serviced. The TCF bit

is cleared by a hardware RESET signal, a software RESET instruction, the

STOP instruction, or by clearing the TCSR[TE] bit to disable the timer.

NOTE: The TOF and TCF bits are cleared by a 1 written to the specific bit.

To ensure that only the target bit is cleared, do not use the BSET

command. The proper way to clear these bits is to write 1, using a MOVEP

instruction, to the flag to be cleared and 0 to the other flag.

20

TOF

0

Timer Overflow Flag

Indicates that a counter overflow has occurred. This bit is cleared by

writing a one to the TOF bit. Writing a zero to TOF has no effect. The bit is

also cleared when the timer overflow interrupt is serviced. The TOF bit is

cleared by a hardware RESET signal, a software RESET instruction, the

STOP instruction, or by clearing the TCSR[TE] bit to disable the timer

.

19–16

0

Reserved. Write to zero for future compatibility.

15

PCE

0

Prescaler Clock Enable

Selects the prescaler clock as the timer source clock. When PCE is

cleared, the timer uses either an internal (CLK/2) signal or an external

(TIO) signal as its source clock. When PCE is set, the prescaler output is

the timer source clock for the counter, regardless of the timer operating

mode. To ensure proper operation, the PCE bit is changed only when the

timer is disabled. The PS[1–0] bits of the TPLR determine which source

clock is used for the prescaler. A timer can be clocked by a prescaler clock

that is derived from the TIO of another timer.

14

0

Reserved. Write to zero for future compatibility.

13

DO

0

Data Output

The source of the TIO value when it is a data output signal. The TIO signal

is a data output when the GPIO mode is enabled and DIR is set. A value

written to the DO bit is written to the TIO signal. If the INV bit is set, the

value of the DO bit is inverted when written to the TIO signal. When the

INV bit is cleared, the value of the DO bit is written directly to the TIO

signal. When GPIO mode is disabled, writing to the DO bit has no effect.

12 DI

0

Data Input

Reflects the value of the TIO signal. If the INV bit is set, the value of the

TIO signal is inverted before it is written to the DI bit. If the INV bit is

cleared, the value of the TIO signal is written directly to the DI bit.

Table 9-3. Timer Control/Status Register (TCSR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description