Motorola DSP56301 User Manual

Page 175

Host-Side Programming Model

Host Interface (HI32)

6

-57

n

In a 16-bit data Universal Bus mode (DCTR[HM]

=

$2 or $3 and HCTR[HRF]

≠

$0),

the HD[15–0] pins are driven with the two least significant bytes of the HSTR in a read

access.

n

In PCI mode (DCTR[HM] = $1) memory space transactions, the HSTR is accessed if

the PCI address is HI32_base_address: $014.

n

In a Universal Bus mode (DCTR[HM]

=

$2 or $3), the HSTR is accessed if the

HA[10–3] value matches the HI32 base address (see Section 6.8.11, Memory Space

Base Address Configuration Register (CBMA), on page 6-70) and the HA[2–0] value

is $5.

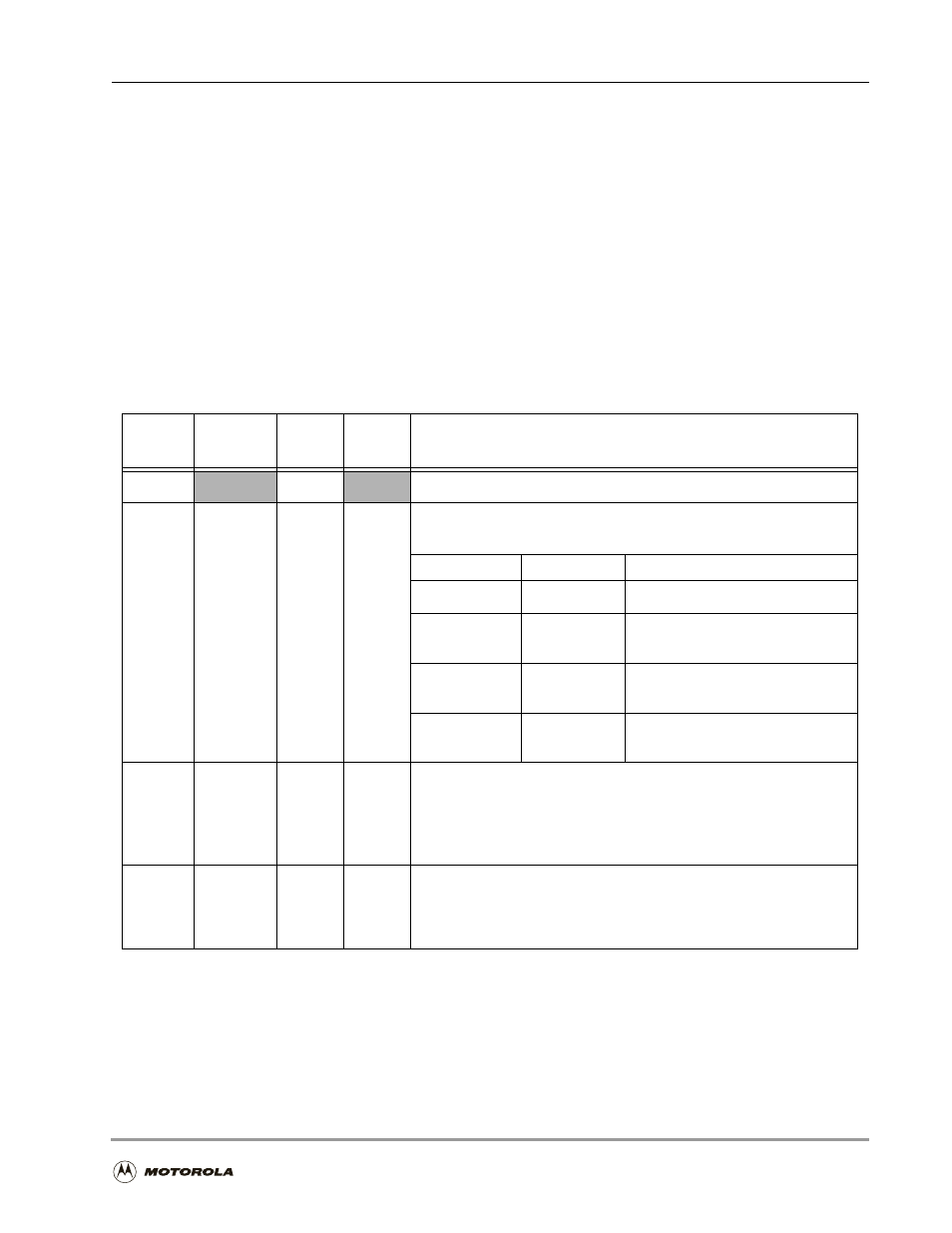

Table 6-23. Host Interface Status Register (HSTR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Mode

Description

31–8

0

Reserved. Write to 0 for future compatibility.

7

HREQ

0

UBM

PCI

Host Request

Set and cleared as follows. The personal software reset clears HREQ.

TREQ

RREQ

HREQ

0

0

cleared

0

1

set if HRRQ = 1

otherwise cleared

1

0

set if HTRQ = 1

otherwise cleared

1

1

set if HTRQ = 1 or HRRQ = 1

otherwise cleared

6

HINT

0

UBM

PCI

Host interrupt A

Reflects the status of the HINT bit in the DSP Control Register (DCTR)

and the HINTA pin. HINT is set if the host interrupt A bit is set in the

DCTR and the HINTA pin is driven low. HINT is cleared if the host

interrupt A is cleared in the DCTR, and the HINTA pin is driven low.

5–3

HF[5–3]

0

UBM

PCI

Host Flags

Indicate the state of host flags HF[5–3], respectively, in the DSP Control

Register (DCTR) on the DSP side. Only the DSP56300 core can

change HF[5–3].