Motorola DSP56301 User Manual

Page 320

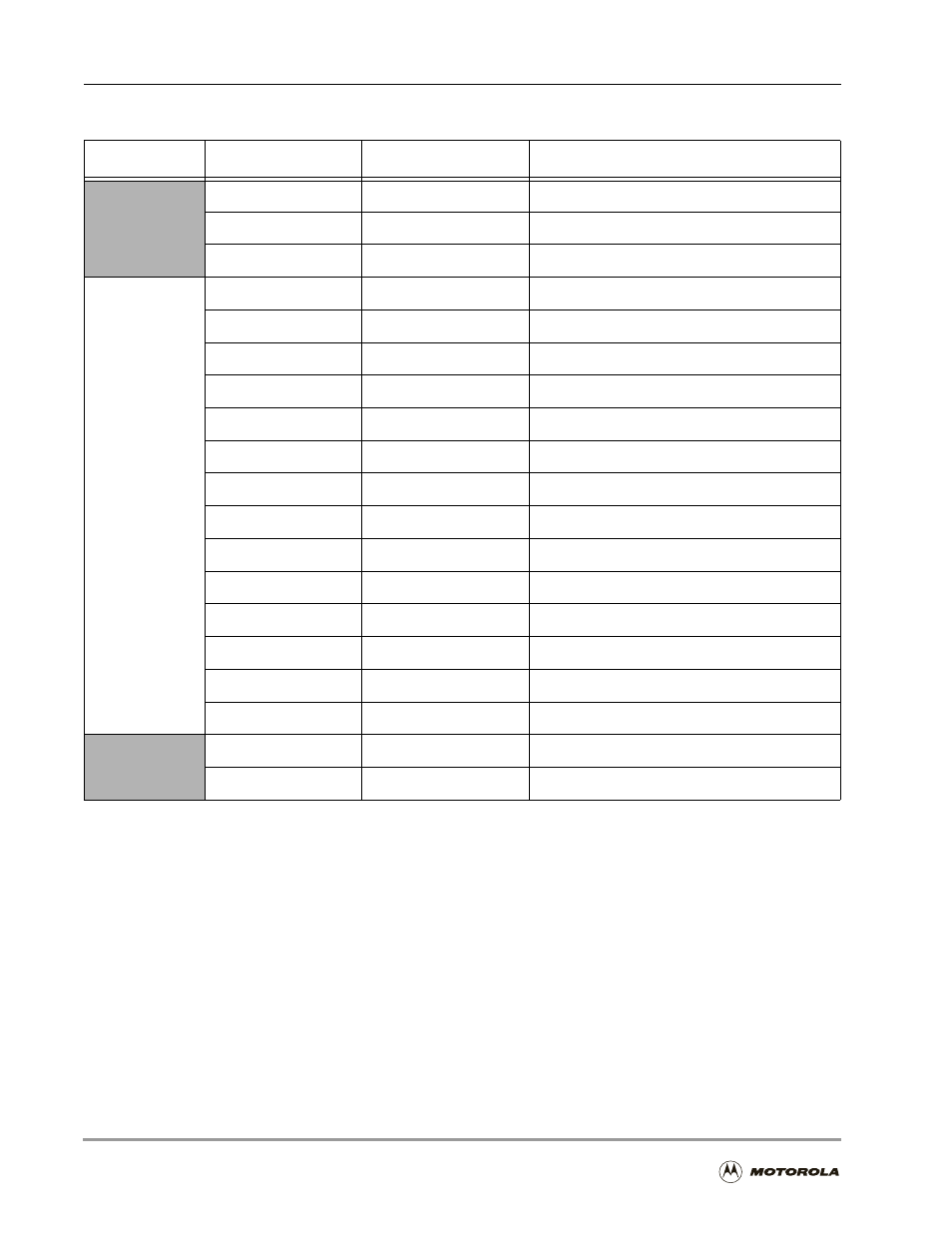

Internal I/O Memory Map

B

-8

DSP56301 User’s Manual

$FF92

$FFFF92

Reserved

$FF91

$FFFF91

Reserved

$FF90

$FFFF90

Reserved

Triple Timer

$FF8F

$FFFF8F

Timer 0 Control/Status Register (TCSR0)

$FF8E

$FFFF8E

Timer 0 Load Register (TLR0)

$FF8D

$FFFF8D

Timer 0 Compare Register (TCPR0)

$FF8C

$FFFF8C

Timer 0 Count Register (TCR0)

$FF8B

$FFFF8B

Timer 1 Control/Status Register (TCSR1)

$FF8A

$FFFF8A

Timer 1 Load Register (TLR1)

$FF89

$FFFF89

Timer 1 Compare Register (TCPR1)

$FF88

$FFFF88

Timer 1 Count Register (TCR1)

$FF87

$FFFF87

Timer 2 Control/Status Register (TCSR2)

$FF86

$FFFF86

Timer 2 Load Register (TLR2)

$FF85

$FFFF85

Timer 2 Compare Register (TCPR2)

$FF84

$FFFF84

Timer 2 Count Register (TCR2)

$FF83

$FFFF83

Timer Prescaler Load Register (TPLR)

$FF82

$FFFF82

Timer Prescaler Count Register (TPCR)

$FF81

$FFFF81

Reserved

$FF80

$FFFF80

Reserved

Table B-2. Internal I/O Memory Map (X Data Memory) (Continued)

Peripheral

16-Bit Address

24-Bit Address

Register Name