Motorola DSP56301 User Manual

Page 173

Host-Side Programming Model

Host Interface (HI32)

6

-55

2

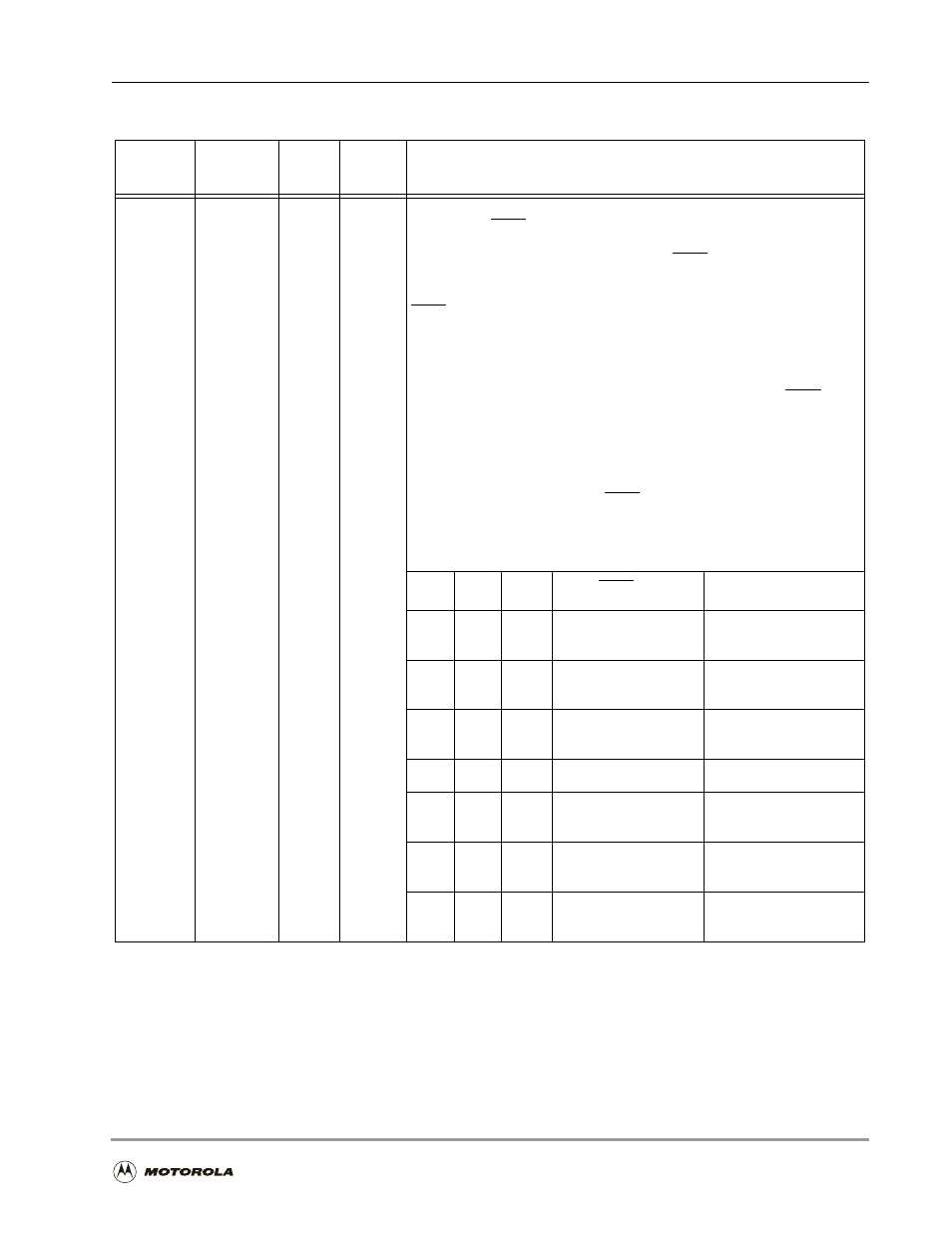

RREQ

0

UBM

Receive Request Enable

Controls the HIRQ and HDRQ pins for DSP-to-host data transfers in a

Universal Bus mode (DCTR[HM]

=

$2 or $3). When DMAE is cleared,

RREQ enables the host interrupt request (HIRQ) pin if the host receive

data request (HRRQ) status bit in the HSTR is set. If RREQ is cleared,

HRRQ host interrupt requests are disabled. The host interrupt request

HIRQ pin is asserted if HRRQ is set. HDRQ is deasserted.

If DMAE is set, RREQ enables the host DMA request (HDRQ) pin when

the host receive data request (HRRQ) status bit in the HSTR is set. If

RREQ is cleared, HRRQ host DMA requests are disabled. If RREQ is set,

the host DMA request HDRQ pin is asserted if HRRQ is set. HIRQ is

deasserted (high impedance) if HIRD = 0 in the DCTR.

Note:

In a Universal Bus mode (DCTR[HM] = $2 or $3), when both

the TREQ and RREQ control bits (in the HCTR) are cleared,

host interrupt request / strobe / acknowledge hardware

handshake (using the HIRQ / Data Strobe / HTA pins) is

disabled. The host can poll the HTRQ, and HSTR[HRRQ] status

bits or use the host data strobe/acknowledge hardware

handshake (using the Data Strobe / HTA pins).

DMAE TREQ RREQ

HIRQ Pin

HDRQ pin

0

0

0

deasserted

2

(HRRQ,

HTRQ polling)

high impedance

0

1

0

HTRQ Host Interrupt

Request Enabled

high impedance

0

1

1

HRRQ, HTRQ Interrupt

Requests Enabled

high impedance

1

0

0

deasserted

1

high impedance

1

0

1

deasserted

1

HRRQ DMA Request

Enabled

1

1

0

deasserted

1

HTRQ DMA Request

Enabled

1

1

1

deasserted

1

HRRQ, HTRQ Host DMA

Requests Enabled

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description