Motorola DSP56301 User Manual

Page 170

Host-Side Programming Model

6

-52

DSP56301 User’s Manual

9–8

cont.

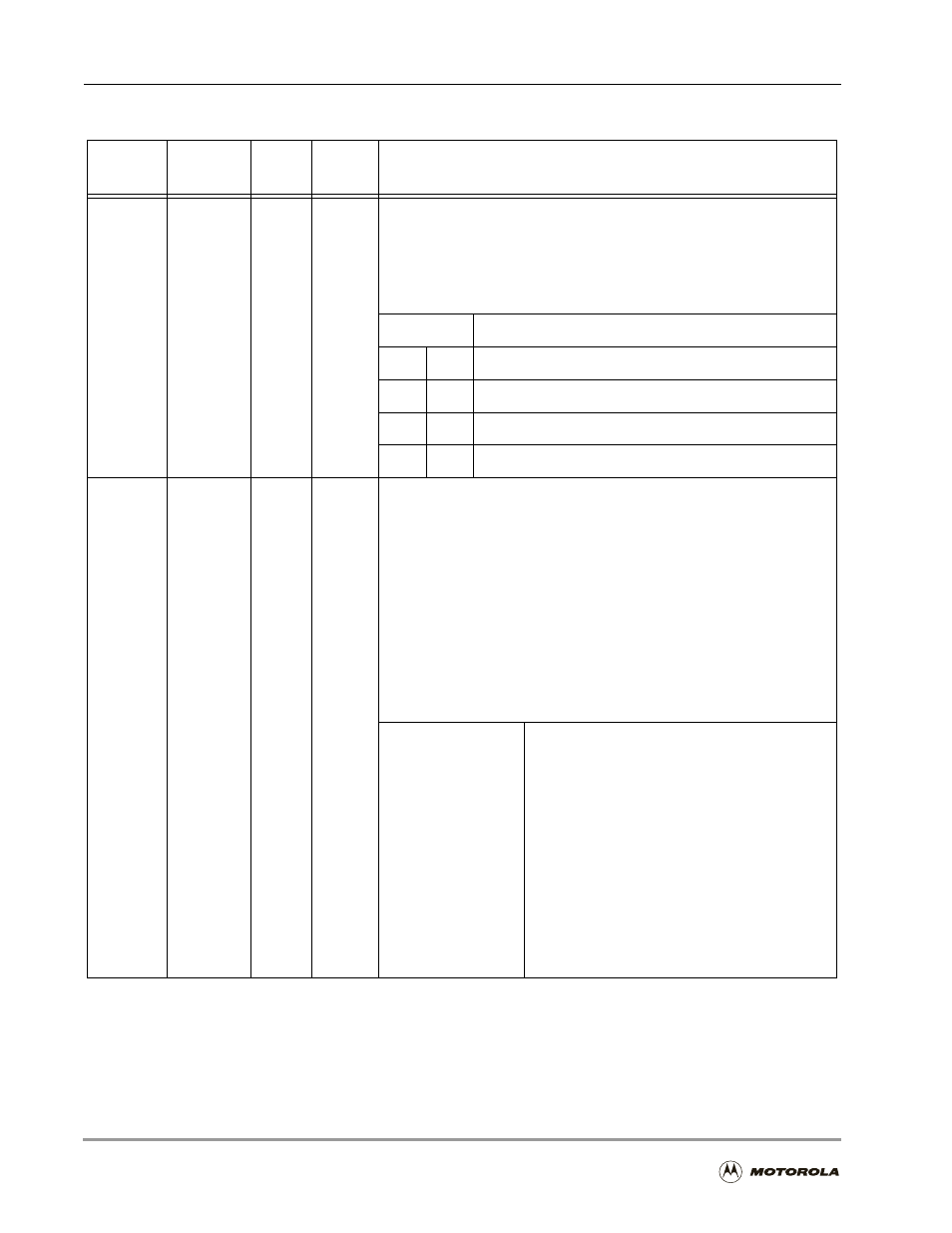

HTF[1–0]

0

UBM

PCI

Host Transmit Data Transfer Format (cont.)

Note:

When the HI32 is in PCI mode, the HTF control bits affect the

address insertion (the IAE bit is set in the DPCR) in the same

way they affect the transferred data.

Address as appears on the PCI bus: $12345678

HTF[1–0]

Inserted Address

0

0

$005678, $001234

0

1

$345678

1

0

$345678

1

1

$123456

7

SFT

0

UBM

PCI

Slave Fetch Type

Defines Fetch mode (data fetch or pre-fetch), as follows:

n

SFT = 1, Fetch

n

SFT = 0, Pre-Fetch

In Fetch mode, the HI32 requests data from the DSP56300 core only

after the host has begun a read transaction from the HI32. The HI32

issues this request by enabling the STRQ status bit and generating core

interrupt requests or DMA requests, if enabled. In Pre-Fetch mode: the

HI32 requests data from the DSP56300 core whenever the DTXS is not

full. The HI32 issues this request by enabling the STRQ status bit and

generating core interrupt requests or DMA requests, if enabled. The

value of SFT can be changed only if the DTXS-HRXS data path is empty.

The personal hardware reset clears SFT.

PCI mode

(DCTR[HM] = $1)

Fetch (SFT = 1):

The DSP-to-host data path (DTXS-HRXS) is a six

word deep (three word deep if HCTR[HRF] = $0)

FIFO buffer. Writing SFT = 1 resets the

DSP-to-host data path and clears STRQ and

HSTR[HRRQ]. During a read transaction from the

HRXS, STRQ is set if the DTXS-HRXS FIFO is

not full, and cleared when the DSP56300 core fills

the DTXS. HSTR[HRRQ] is cleared if the HRXS

is empty, and set if it contains data to be read by

an external host. If the host is not executing a

read transaction from the HRXS, the DSP-to-host

data path is forced to the reset state and STRQ

and HSTR[HRRQ] are cleared.

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description