Motorola DSP56301 User Manual

Page 121

Features

Host Interface (HI32)

6

-3

Handshaking

Protocols

n

Software polled

n

Interrupt driven (fast or long)

n

Direct Memory Access (up to six

DSP56300 core DMA channels)

Universal Bus mode:

n

Software Polled

n

Interrupt Driven—Data Request (HIRQ

pin) and Interrupt A (HINTA pin)

n

Data Acknowledge (

HTA

pin)

n

Direct Memory Access (External

DMA—HDRQ and HDAK pins)

PCI mode:

n

Software polled (PCI Interrupt (HINTA

pin))

n

Data Acknowledge (HTRDY and HIRDY

pins)

n

Bus Arbitration (HREQ and HGNT)

GPIO

24 I/O pins (data and pin direction are

programmable)

Self

Configuration

Indirect write-only access of DSP56300 core to

the HI32 configuration registers

Instructions

Memory-mapped registers allow standard

MOVE instruction for data transfers between the

DSP56301 and external hosts; special MOVEP

instruction provides I/O service capability using

fast interrupts and faster execution with fewer

instruction words

Address

Decoding

n

PCI Mode: 32-bit internal address

decoding

n

Universal Bus mode: 11-bit (12 with

HAEN) internal address decoding

Data Fetch

Types

In HI32 (slave) to host data transfers: fetch and

pre-fetch

Semaphores

Flags for HI32 allocation in a multi-host system

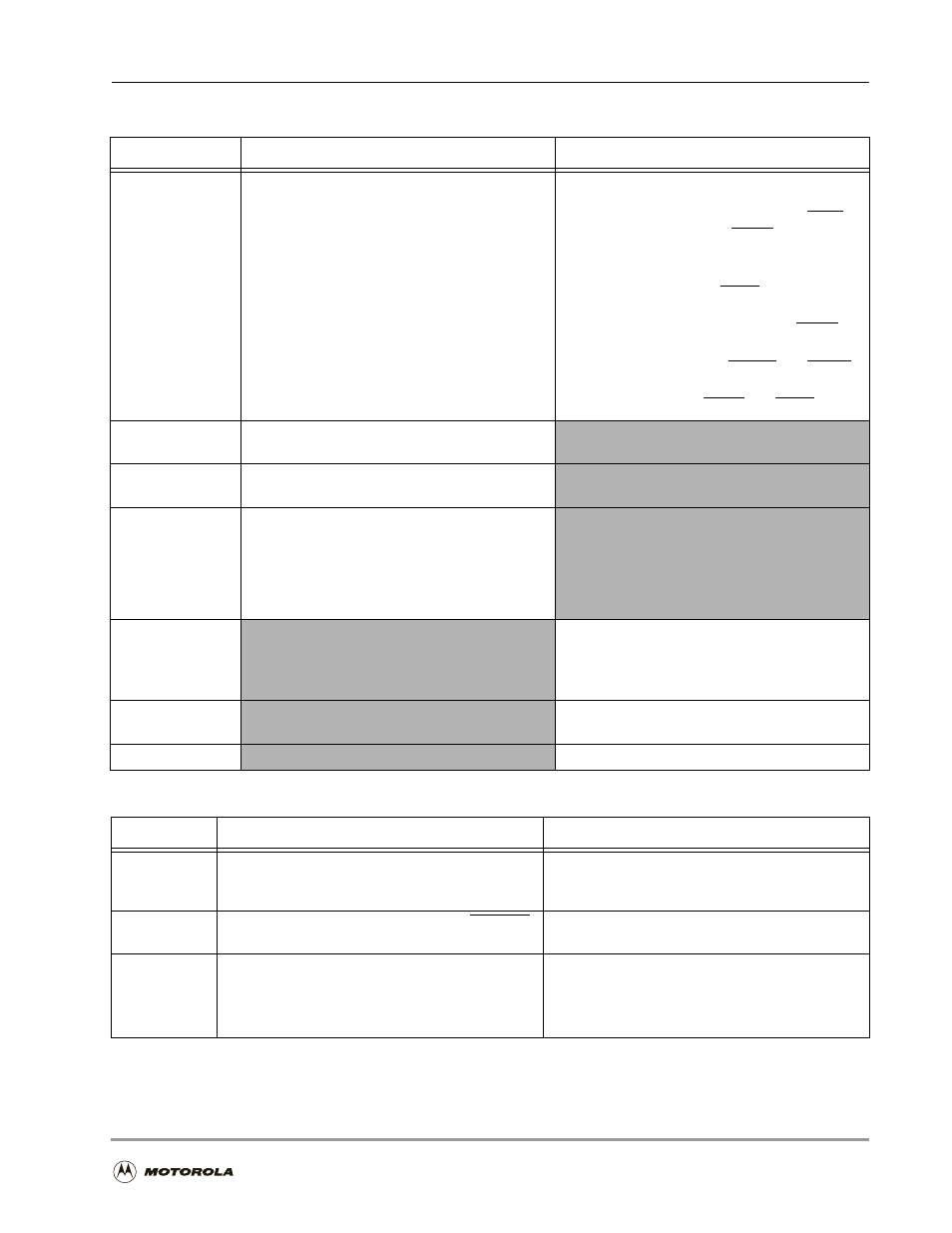

Table 6-2. HI32 Features in PCI Mode and Universal Bus Mode

Feature

PCI Mode

Universal Bus Mode

Operation

Initiator (master) or target (slave)

Slave in many standard bus environments (for

example, ISA bus or DSP56300 core-based DSP

Port A bus)

Word Size

8,16, 24, and 32 bits (as defined by the HBE[3–0]

lines)

8,16, and 24 bits wide.

Input Data

Alignment

32-bit words to 24 bit words:

n

Three MSBs

n

Three LSBs

16-bit words to 24-bit words

n

Left aligned and zero filled

n

Right aligned and zero extended

n

Right aligned and sign extended

Table 6-1. HI32 Features, Core-Side and Host-Side (Continued)

Feature

Core-Side Interface

Host-Side Interface