4 reset states, 5 dsp-side operating modes, Reset states -12 – Motorola DSP56301 User Manual

Page 130: Dsp-side operating modes -12, Hi32 reset -12, 4 reset states, 5 dsp-side operating modes, Table 6-6 describes the various hi32 reset states

Reset States

6

-12

DSP56301 User’s Manual

6.4

Reset States

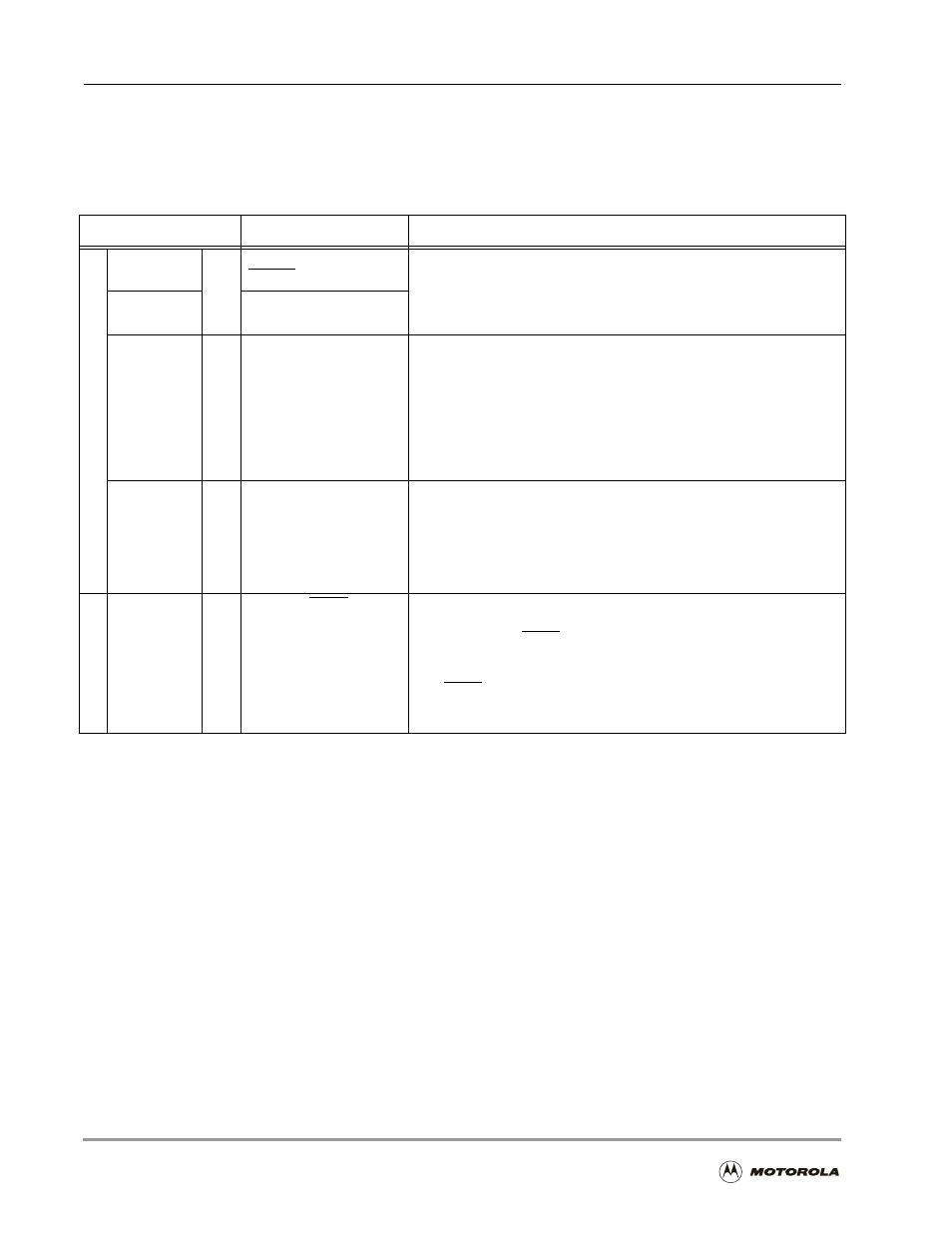

Table 6-6 describes the various HI32 reset states.

6.5

DSP-Side Operating Modes

The HI32 Mode (DCTR[HM]) bits in the DSP Control Register (DCTR) control the HI32

operating modes (see Table 6-10, DSP Control Register (DCTR) Bit Definitions, on

page 6-23). The DSP56300 core can change the value of the DCTR[HM] bits only when the

HI32 is in the personal software reset state (DCTR[HM] = $0, DSR[HACT] = 0). These

bits must not be changed together (that is, in the same core write) with any of the following

bits: HDSM, HRWP, HTAP, HDRP, HRSP, HIRH, or HIRD. The combinations DCTR[HM]

= $6, DCTR[HM] = $7 are reserved for future expansion and should not be used.

Table 6-6. HI32 Reset

Type

Entered when

Description

In

iti

a

te

d b

y

th

e D

SP5

630

0 C

o

re

Hardware

Reset

HS

The DSP56300 core

RESET pin is asserted.

These resets force the HI32 DSP side state machines, control

registers, and status registers to their initial states. These resets also

activate the Personal Software (PS) reset.

Software

Reset

The RESET instruction

is executed.

Personal

Software

Reset

PS

The DSP56300 core

writes zeros to the HI32

mode bits HM[2–0] in

the DSP control register

or the HS reset has

executed.

The HI32 terminates the current PCI transaction (if it is an active PCI

agent), clears the HACT bit in the DSP Status Register (DSR) and

enters the personal software (PS) reset state. All data paths are

cleared. In the personal software reset state, the HI32 is a PCI agent

and responds to all memory and configuration space transactions

with a retry event. If connected to other buses (for example, ISA bus,

DSP56300 core-based DSP Port A bus, and so on) all outputs are

high impedance.

STOP mode

ST

The STOP instruction

executes.

This reset forces all host port pins to the disconnected state: all

outputs are high impedance, all inputs are electrically disconnected.

The host port pins are affected immediately.

Note:

This mode can execute only when the HACT bit in the DSP

Status Register (DSR) is zero.

In

iti

a

te

d b

y

t

he H

o

st

Personal

Hardware

Reset

PH

The HI32 HRST/HRST

pin is asserted.

This reset forces the HI32 host-side state machines, control

registers, and configuration registers to their initial states. All host

port pins, except HRST/HRST, are forced to the disconnected state:

all outputs are high impedance, all inputs are electrically

disconnected. The DSP-side state machines are not affected.

The HRST/HRST pin is ignored in Self-Configuration mode.