Motorola DSP56301 User Manual

Page 195

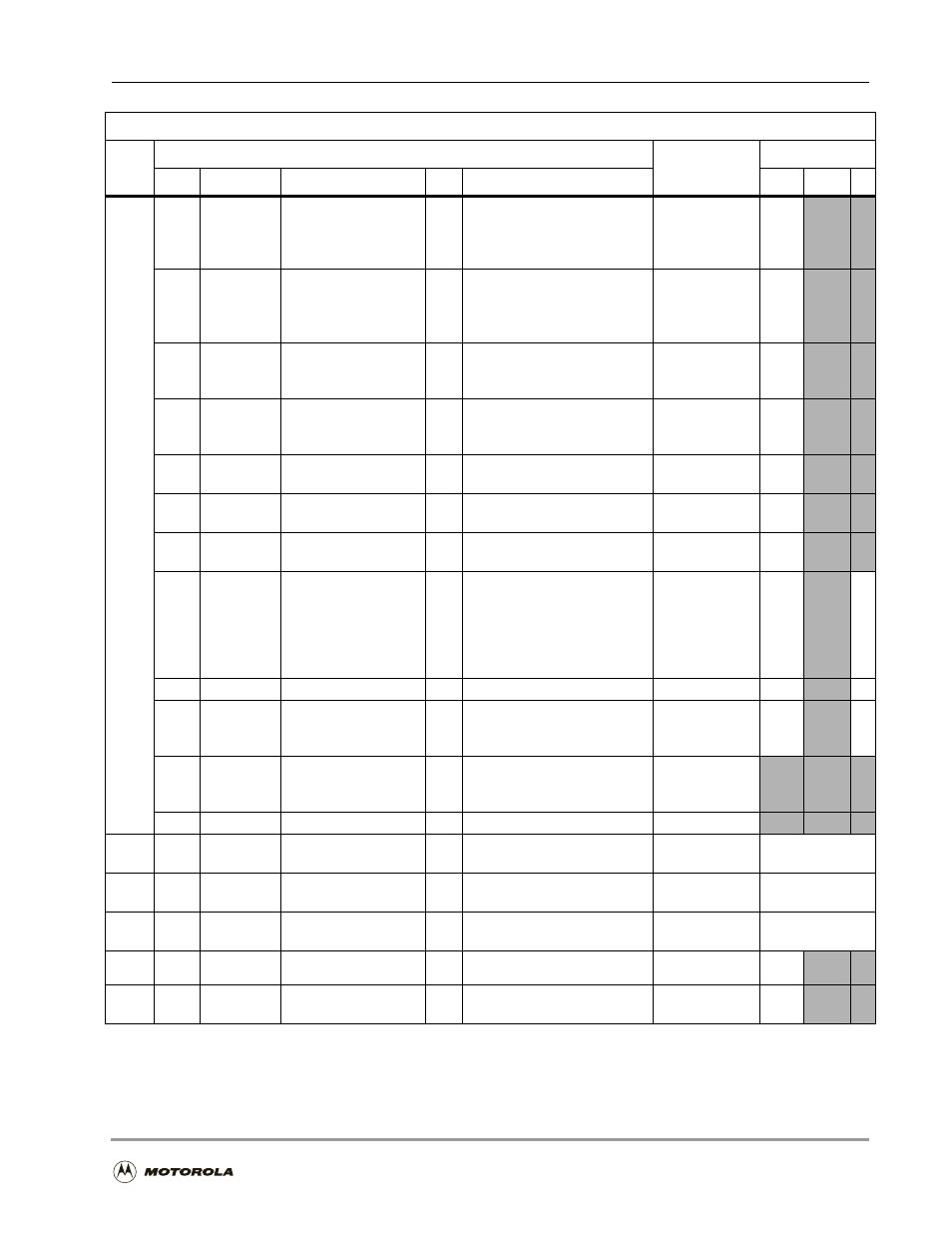

HI32 Programming Model/Quick Reference

Host Interface (HI32)

6

-77

DPSR

cont.

5

APER

PCI Address Parity

Error

0

1

HI32 target has not detected

an address parity error

HI32 target has detected an

address parity error

cleared by

writing 1

0

-

-

6

DPER

PCI Data Parity Error

0

1

a data parity error has not

occurred

a data parity error has

occurred

cleared by

writing 1

0

-

-

7

MAB

PCI Master Abort

0

1

a master abort has not

occurred

a master abort has occurred

cleared by

writing 1

0

-

-

8

TAB

PCI Target Abort

0

1

a target abort has not

occurred

a target abort has occurred

cleared by

writing 1

0

-

-

9

TDIS

PCI Target Disconnect

0

1

no target disconnect

a target disconnect

cleared by

writing 1

0

-

-

10

TRTY

PCI Target Retry

0

1

no target retry

a target retry

cleared by

writing 1

0

-

-

11

TO

PCI Time Out

Termination

0

1

no time-out termination

a time-out termination

cleared by

writing 1

0

-

-

12

HDTC

PCI Host Data

Transfer Complete

0

1

HI32 is transferring data to the

core

HI32 has completed transfer

of data to the core and will

disconnect write accesses to

the HTXR

cleared by

writing 1; written

1 only if HDTC =

1

0

-

0

13

14

MDT

Master Data

Transferred

0

1

No data transfer; all data did

not transfer successfully

Data transferred successfully

0

0

15

RDCQ

Remaining Data Count

Qualifier

0

1

No data transfer; data

transferred successfully

Qualify RDC[5–0] value

-

-

-

21–16

RDC[5–0] Remaining Data Count

BL[5–0] = RDC[5–0] + RDCQ

-

-

-

DRXR

23–0

DSP Receive Data

FIFO

empty

DTXM

23–0

DSP Master Transmit

Data FIFO

empty

DTXS

23–0

DSP Slave

Transmit Data FIFO

empty

DATH

23–0

DAT[23–0] GPIO Pin Data

$0000

00

-

-

DIRH

23–0

DIR[23–0] GPIO Pin Direction

0

1

Input

Output

$0000

00

-

-

HI32 Registers—Quick Reference

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HS

PH

PS