Motorola DSP56301 User Manual

Page 104

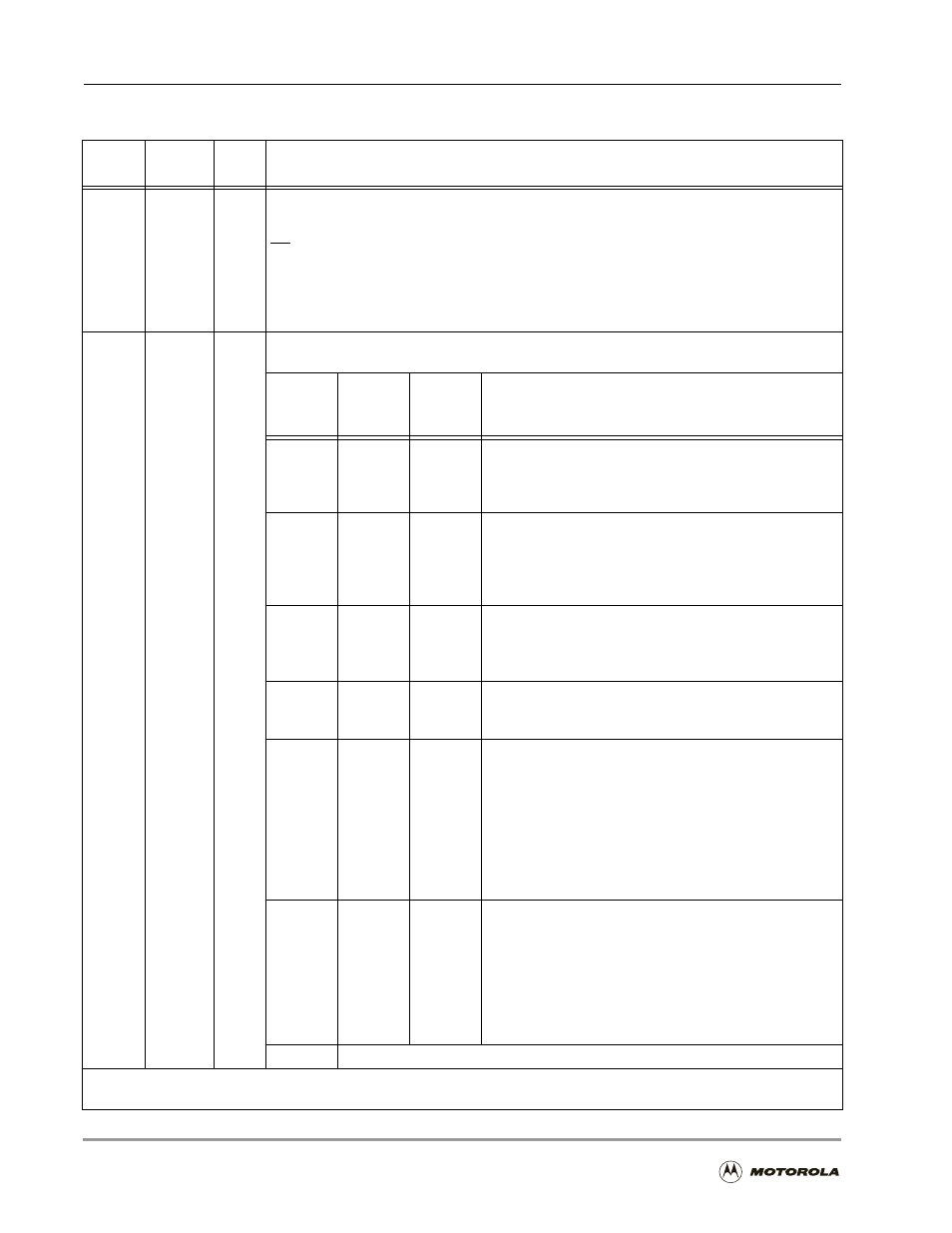

DMA Control Registers 5–0 (DCR[5–0])

4

-30

DSP56301 User’s Manual

22

DIE

0

DMA Interrupt Enable

Generates a DMA interrupt at the end of a DMA block transfer after the counter is loaded

with its preloaded value. A DMA interrupt is also generated when software explicitly clears

DE during a DMA operation. Once asserted, a DMA interrupt request can be cleared only by

the service of a DMA interrupt routine. To ensure that a new interrupt request is not

generated, clear DIE while the DMA interrupt is serviced and before a new DMA request is

generated at the end of a DMA block transfer—that is, at the beginning of the DMA channel

interrupt service routine. When DIE is cleared, the DMA interrupt is disabled.

21–19

DTM[2–0]

0

DMA Transfer Mode

Specify the operating modes of the DMA channel, as follows:

DTM[2–0]

Trigger

DE

Cleared

After

Transfer Mode

000

request

Yes

Block Transfer—DE enabled and DMA request initiated.

The transfer is complete when the counter decrements to

zero and the DMA controller reloads the counter with the

original value.

001

request

Yes

Word Transfer—A word-by-word block transfer (length

set by the counter) that is DE enabled. The transfer is

complete when the counter decrements to zero and the

DMA controller reloads the counter with the original

value.

010

request

Yes

Line Transfer—A line by line block transfer (length set by

the counter) that is DE enabled. The transfer is complete

when the counter decrements to zero and the DMA

controller reloads the counter with the original value.

011

DE

Yes

Block Transfer—The DE-initiated transfer is complete

when the counter decrements to zero and the DMA

controller reloads the counter with the original value.

100

request

No

Block Transfer—The transfer is enabled by DE and

initiated by the first DMA request. The transfer is

completed when the counter decrements to zero and

reloads itself with the original value. The DE bit is not

cleared at the end of the block, so the DMA channel waits

for a new request.

Note:

The DMA End-of-Block-Transfer Interrupt

cannot be used in this mode.

101

request

No

Word Transfer—The transfer is enabled by DE and

initiated by every DMA request. When the counter

decrements to zero, it is reloaded with its original value.

The DE bit is not automatically cleared, so the DMA

channel waits for a new request.

Note:

The DMA End-of-Block-Transfer Interrupt

cannot be used in this mode.

110–111

Reserved

Note:

When DTM[2–0] = 001 or 101, some peripherals can generate a second DMA request while the DMA controller is

still processing the first request (see the description of the DRS bits).

Table 4-12. DMA Control Register (DCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description