Motorola DSP56301 User Manual

Page 56

Enhanced Synchronous Serial Interface 1

2

-26

DSP56301 User’s Manual

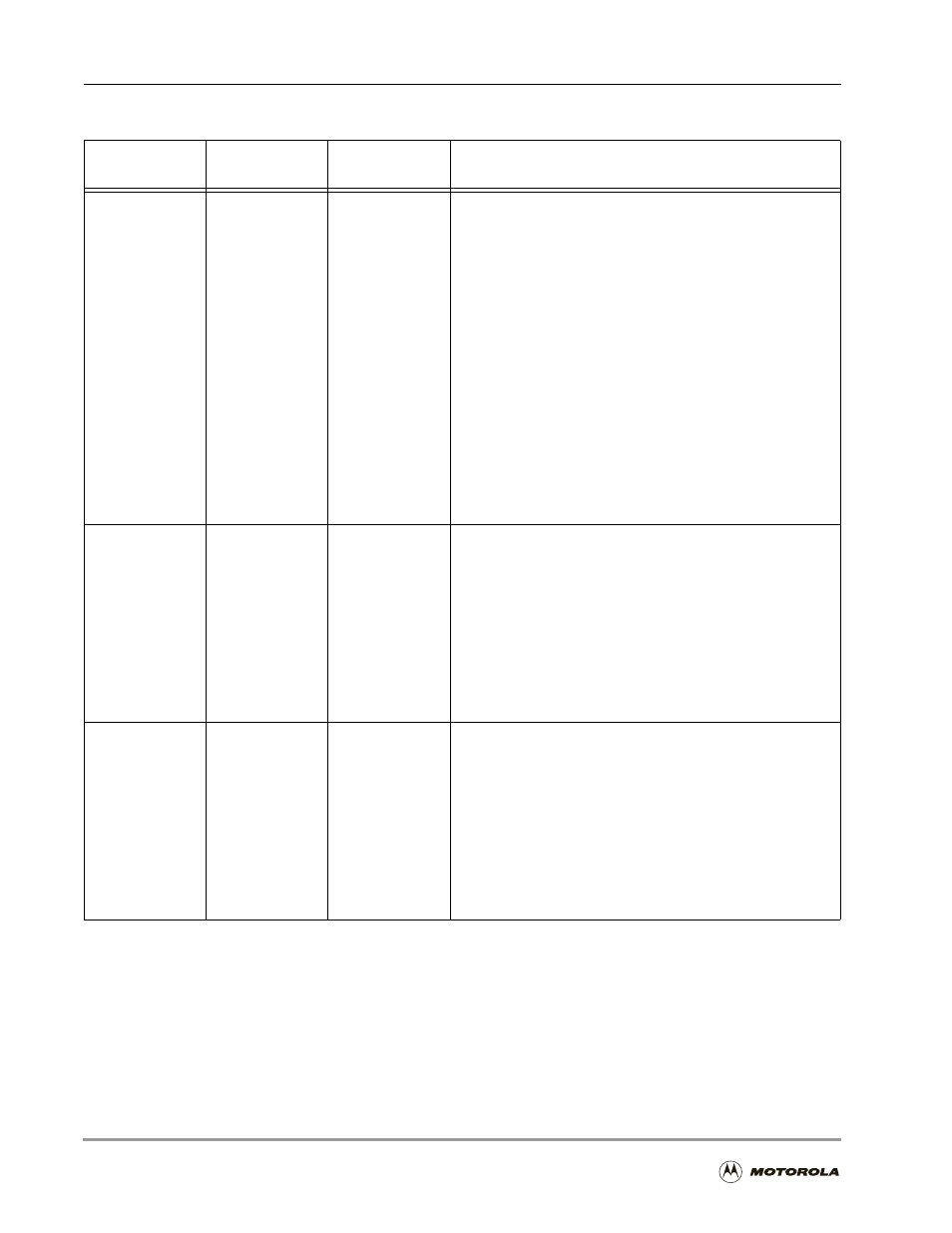

SCK1

PD3

Input/

Output

Input or Output

Input

Serial Clock—Provides the serial bit rate clock for the ESSI.

The SCK1 is a clock input or output used by both the

transmitter and receiver in synchronous modes, or by the

transmitter in asynchronous modes.

Although an external serial clock can be independent of and

asynchronous to the DSP system clock, it must exceed the

minimum clock cycle time of 6T (that is, the system clock

frequency must be at least three times the external ESSI

clock frequency). The ESSI needs at least three DSP phases

inside each half of the serial clock.

Port D 3—The default configuration following reset is GPIO

input PD3. When configured as PD3, signal direction is

controlled through PRR1. The signal can be configured as an

ESSI signal SCK1 through PCR1.

This signal has a weak keeper to maintain the last state even

if all drivers are tri-stated.

SRD1

PD4

Input/

Output

Input or Output

Input

Serial Receive Data—Receives serial data and transfers the

data to the ESSI receive shift register. SRD1 is an input when

data is being received.

Port D 4—The default configuration following reset is GPIO

input PD4. When configured as PD4, signal direction is

controlled through PRR1. The signal can be configured as an

ESSI signal SRD1 through PCR1.

This signal has a weak keeper to maintain the last state even

if all drivers are tri-stated.

STD1

PD5

Input/

Output

Input or Output

Input

Serial Transmit Data—Transmits data from the serial

transmit shift register. STD1 is an output when data is being

transmitted.

Port D 5—The default configuration following reset is GPIO

input PD5. When configured as PD5, signal direction is

controlled through PRR1. The signal can be configured as an

ESSI signal STD1 through PCR1.

This signal has a weak keeper to maintain the last state even

if all drivers are tri-stated.

Table 2-14. Enhanced Serial Synchronous Interface 1 (Continued)

Signal Name

Type

State During

Reset

Signal Description