7 host interface (hi32), Host interface (hi32) -10, Device identification register (idr) -34 – Motorola DSP56301 User Manual

Page 40: Host interface -10, 7 host interface (hi32)

Host Interface (HI32)

2

-10

DSP56301 User’s Manual

2.7

Host Interface (HI32)

The Host Interface (HI32) provides a fast parallel data port up to 32 bits wide that can connect

directly to the host bus. The HI32 supports a variety of standard buses and provides glueless

connection with the PCI bus standard and with a number of industry-standard

microcomputers, microprocessors, DSPs and DMA hardware. The functions of the signals

associated with the HI32 vary according to the programmed configuration of the interface as

determined by the 24-bit DSP Control Register (DCTR). Refer to Chapter 6, Host Interface

(HI32) for detailed descriptions of this and other HI32 configuration registers.

Note:

All HI32 inputs are 5 V tolerant.

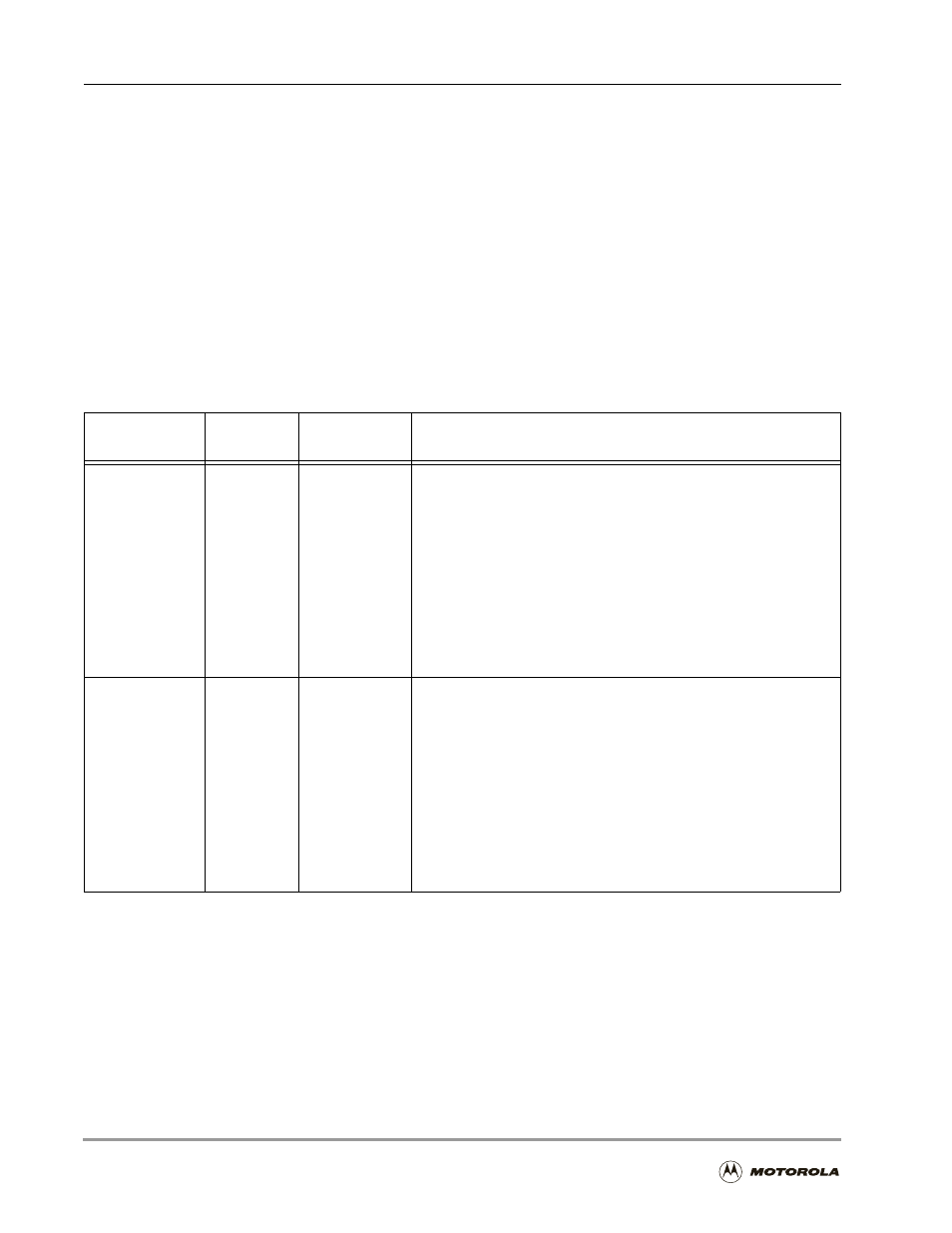

Table 2-10. Host Interface

Signal Name

Type

State During

Reset

Signal Description

HAD[0–7]

HA[3–10]

PB[0–7]

Input/Output

Input

Input or

Output

Tri-stated

Host Address/Data 0–7—When the HI32 is programmed to

interface with a PCI bus and the HI function is selected, these

signals are lines 0–7 of the bidirectional, multiplexed Address/Data

bus.

Host Address 3–10—When HI32 is programmed to interface with a

universal non-PCI bus and the HI function is selected, these signals

are lines 3–10 of the input Address bus.

Port B 0–7—When the HI32 is configured as GPIO through the

DCTR, these signals are individually programmed as inputs or

outputs through the HI32 Data Direction Register (DIRH).

HAD[15–8]

HD[7–0]

PB[15–8]

Input/Output

Input/Output

Input or

Output

Tri-stated

Host Address/Data 8–15—When the HI32 is programmed to

interface with a PCI bus and the HI function is selected, these

signals are lines15–8 of the bidirectional, multiplexed Address/Data

bus.

Host Data 0–7—When the HI32 is programmed to interface with a

universal non-PCI bus and the HI function is selected, these signals

are lines 7–0 of the bidirectional Data bus.

Port B 8–15—When the HI32 is configured as GPIO through the

DCTR, these signals are individually programmed as inputs or

outputs through the HI32 DIRH.