Motorola DSP56301 User Manual

Page 47

Host Interface (HI32)

Signals/Connections

2

-17

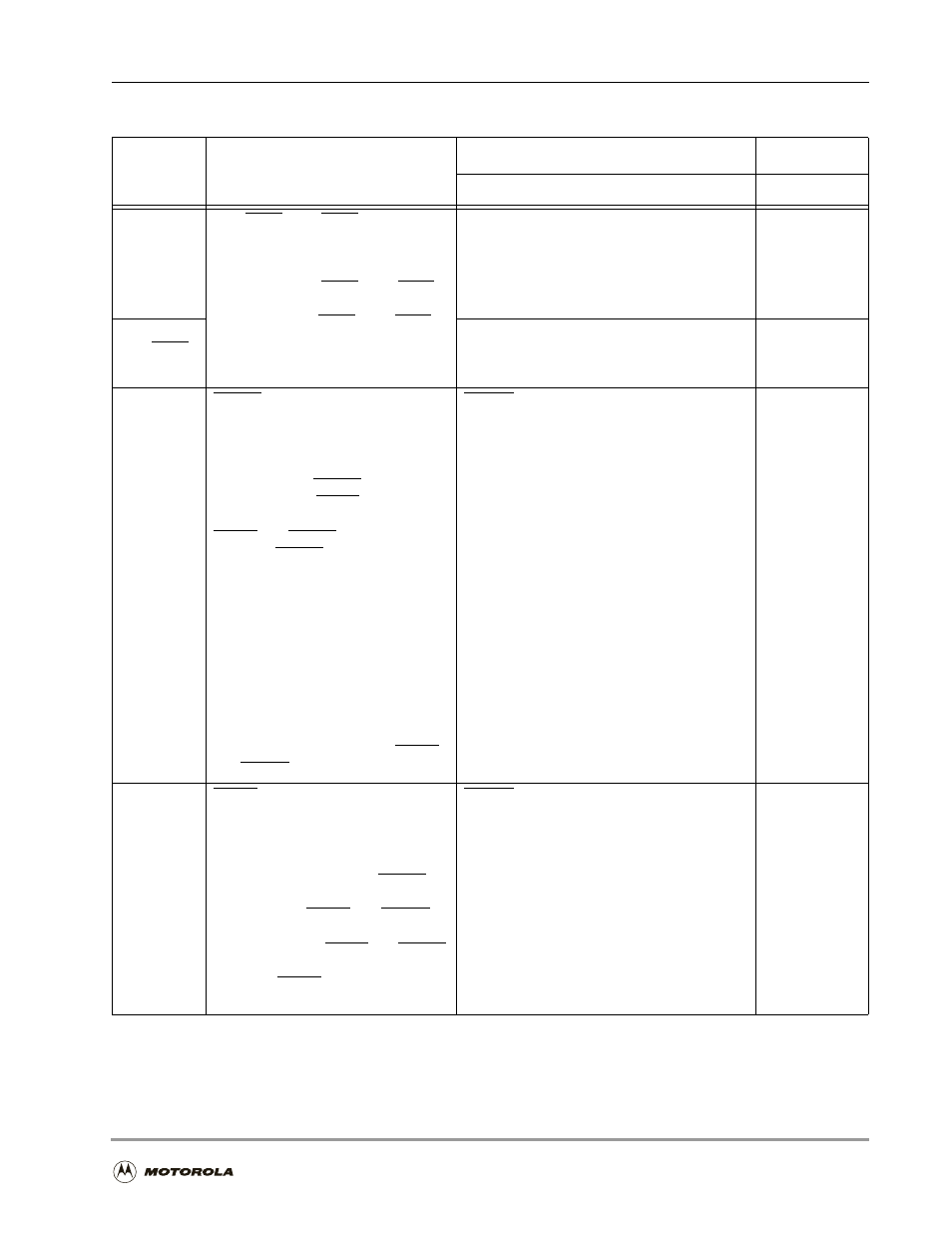

HP[18–16]

HC3/HBE3–HC0/HBE0

Bus Command/Byte Enable

Tri-state bidirectional bus.

During the address phase of a

transaction, HC3/HBE3–HC0/HBE0

define the bus command. During the

data phase HC3/HBE3–HC0/HBE0

are used as byte enables. The byte

enables determine which byte lanes

carry meaningful data.

HA[2–0]

Host Address Bus

Input pin.

Selects HI32 register to access. HA[10–3]

select the HI32 and HA[2–0] select the

particular register of the HI32 to be accessed.

HIO[18–16]

GPIO

2

HP19

HC3/HBE3

Reserved

Must be forced or pulled to V

CC

or GND.

HIO19

GPIO

2

HP20

HTRDY

Host Target Ready

Sustained tri-state bidirectional pin.

2

Indicates the target agent’s ability to

complete the current data phase of

the transaction. HTRDY is used in

conjunction with HIRDY. When a data

phase is completed on any clock both

HIRDY and HTRDY are sampled

asserted. HTRDY is asserted if:

n

during a data read valid data is

present on HAD31-HAD0

(HRRQ=1 in the HSTR).

n

during a data write it indicates

the HI32 is ready to accept

data (HTRQ=1 in the HSTR).

n

during a vector write it indicates

the HI32 is ready to accept a

new host command (HC=0 in

the HCVR).

Wait cycles are inserted until HIRDY

and HTRDY are asserted together.

HDBEN

Host Data Bus Enable

Output pin.

Asserted during HI32 accesses.

When asserted the external (optional) data

transceiver outputs are enabled. When

deasserted the external transceiver outputs

are high impedance.

HIO20

GPIO

2

HP21

HIRDY

Host Initiator Ready

Sustained tri-state bidirectional pin.

2

Indicates the initiating agent’s ability

to complete the current data phase of

the transaction. Used with HTRDY.

When a data phase is completed on

any clock both HIRDY and HTRDY

are sampled asserted. Wait cycles are

inserted until both HIRDY and HTRDY

are asserted together. The HI32

deasserts HIRDY if it cannot complete

the next data phase.

HDBDR

Host Data Bus Direction

Output pin.

Driven high on write data transfers and driven

low on read data transfers. This pin is

normally high.

HIO21

GPIO

2

Table 2-12. Host Port Pins (HI32) (Continued)

Signal

Name

PCI

Universal Bus Mode

Enhanced Universal Bus Mode

GPIO