Motorola DSP56301 User Manual

Page 51

Host Interface (HI32)

Signals/Connections

2

-21

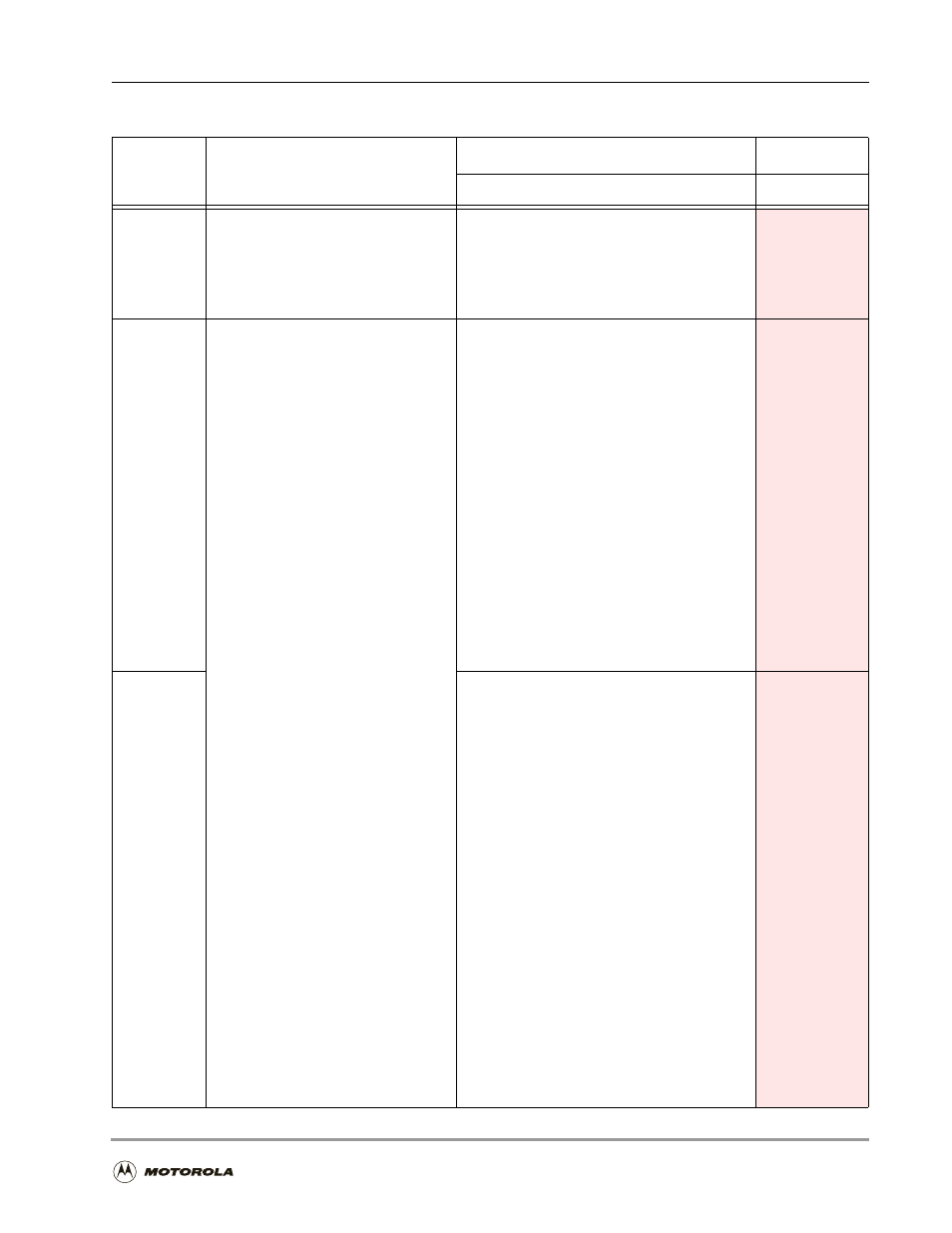

HP32

HCLK

Host Bus Clock

Input pin.

Provides timing for all transactions on

PCI. All other PCI signals are

sampled on the HCLK rising edge.

Reserved.

Must be forced or pulled up to V

CC

.

disconnected

HP[40–33]

HAD[31–16]

Address/Data Multiplexed Bus

Tri-state bidirectional bus.

During the first clock of a transaction

HAD[31–16] contain the physical byte

address (32 bits). During subsequent

clock HAD[31–16] contain data.

HD[23–8]

Data Bus

Tri-state bidirectional bus.

Transfers data between the host processor

and the HI32. This bus is released

(disconnected) when the HI32 is not selected

by HA[10–0]. The HD[23–0] pins are driven by

the HI32 during a read access, and are inputs

to the HI32 during a write access.

During operation with a host bus less than 16

bits wide, the HD[23–8] pins not used to

transfer data must be pulled to Vcc or GND.

For example: during operation with an 8-bit

bus, HP[40–33] must be pulled up to Vcc or

pulled down to GND.

Note: Motorola recommends that you pull

these unused data lines down. Pulling these

lines up sets the corresponding bits when the

external host writes to the HCTR.

disconnected

HP[48–41]

HD[23–16]

Data Bus

Tri-state bidirectional bus.

Transfers data between the host processor

and the HI32.

This bus is released (disconnected) when the

HI32 is not selected by HA[10–0]. The

HD[23–16] pins are driven by the HI32 during

a read access and are inputs to the HI32

during a write access.

HD[23–16] outputs are high impedance if

HRF

≠

$0. HD[23–16] inputs are disconnected

if HTF

≠

$0.

During operation with a host bus less than 24

bits wide, the data pins not used to transfer

data must be forced or pulled to Vcc or to

GND. For example: during operations with a

16-bit bus (for example, ISA bus), HP[48–41]

must be forced or pulled up to V

CC

or pulled

down to GND.

Note: Motorola recommends that you pull

these unused data lines down. Pulling the

lines up sets the corresponding bits when the

external host writes to the HCTR.

disconnected

Table 2-12. Host Port Pins (HI32) (Continued)

Signal

Name

PCI

Universal Bus Mode

Enhanced Universal Bus Mode

GPIO