Motorola DSP56301 User Manual

Page 158

HI32 DSP-Side Programming Model

6

-40

DSP56301 User’s Manual

9

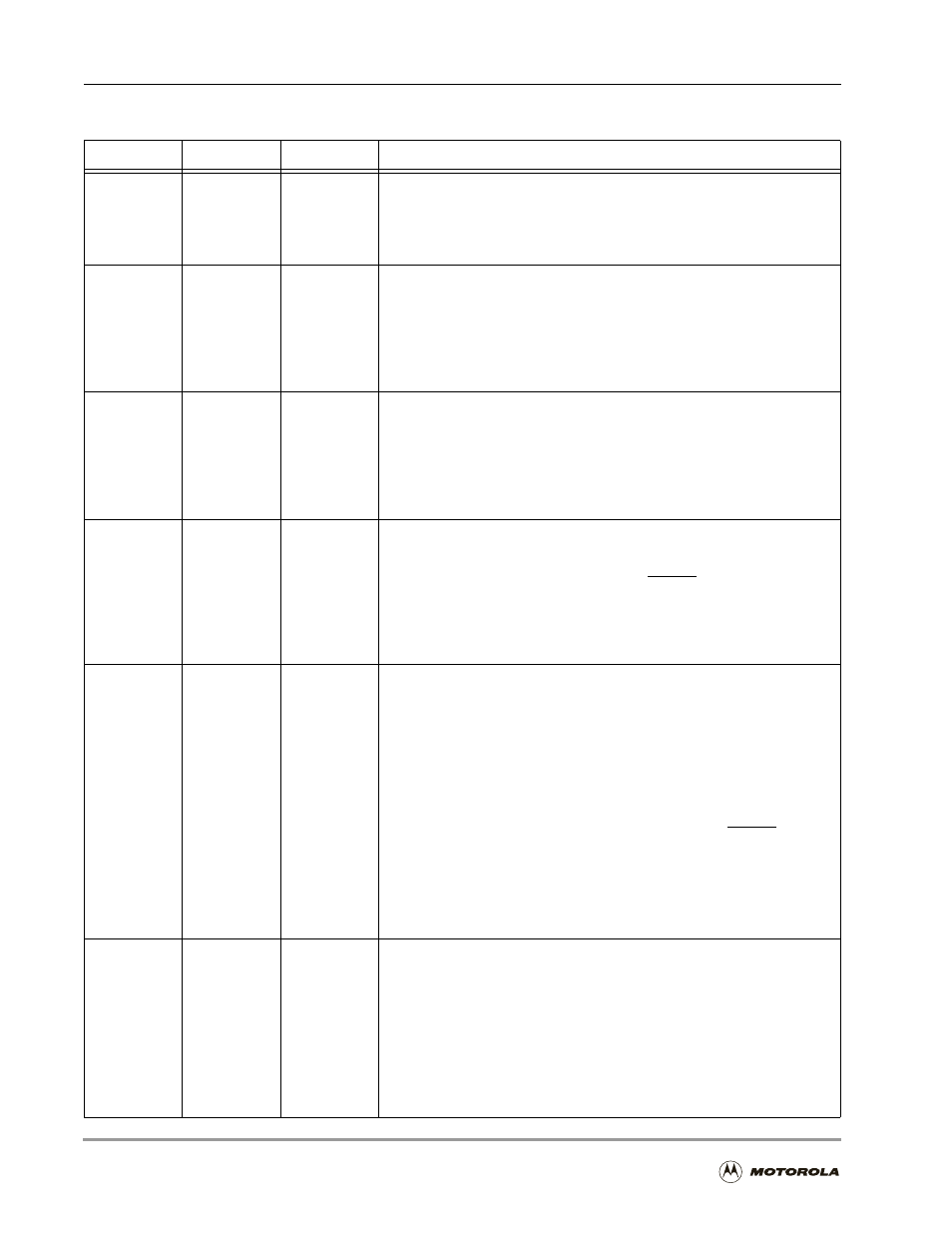

TDIS

0

PCI Target Disconnect

Indicates that an HI32-initiated PCI transaction has terminated with a

target-initiated disconnect. When TDIS is set and, if DPCR[TTIE] is set, a

transaction termination interrupt request is generated. TDIS is cleared

when the DSP56300 core writes a value of one to it.

8

TAB

0

PCI Target Abort

Indicates that an HI32-initiated PCI transaction has terminated with target

abort. When TAB is set and DPCR[TAIE] is set, a transaction abort

interrupt request is generated. TAB is cleared when the DSP56300 core

writes a value of one to it. If an HI32-initiated PCI transaction terminates

with target abort, the received target abort bit (RTA) in the CSTR is also

set.

7

MAB

0

PCI Master Abort

Indicates that an HI32-initiated PCI transaction has terminated with

master abort. MAB is set and, if DPCR[TAIE] is set, generates a

transaction abort interrupt request. MAB is cleared when the DSP56300

core writes a value of one to it. If an HI32-initiated PCI transaction

terminates with a master abort, the received master abort bit (RMA) in the

CSTR is also set.

6

DPER

0

PCI Data Parity Error

In PCI mode (DCTR[HM] = $1) when the HI32 is a PCI master or selected

target, indicates that a data parity error has been detected by the HI32

hardware or reported by the external host (HPERR asserted). At the end

of a transaction, if a data parity error is detected, DPER is set and, if

DPCR[PEIE] is set, a parity error interrupt request is generated. DPER is

cleared when the DSP56300 core writes a value of one to it. In personal

software reset DPER does not reflect new data parity errors.

5

APER

0

PCI Address Parity Error

In PCI mode (DCTR[HM]

=

$1) when the HI32 is a PCI target, indicates

that the HI32 hardware has detected an address parity error. At the end of

a transaction, if an address parity error is detected, APER is set and, if

DPCR[PEIE] is set, a parity error interrupt request is generated. If an

address parity error is detected:

n

The HI32 target claims the cycles and terminates as though the

address was correct.

n

If the system error enable (SERE) bit in the Status/Command

Configuration Register (CSTR/CCMR) is set, the HSERR pin is

pulsed one PCI clock cycle, and the signalled system error (SSE)

bit is set in the CSTR/CCMR.

n

The detected parity error bit (DPE) in the CSTR is set.

APER is cleared when the DSP56300 core writes a value of one to it. In

personal software reset, APER does not reflect new address parity errors.

4

MARQ

0

PCI Master Address Request

Indicates that the HI32 is not the initiator of a PCI transaction and that the

DPAR can be written with the address of the next transaction. When the

PCI bus master enable bit (BM) is set in the CCMR and the HI32 is first

programmed to the PCI mode (DCTR[HM]

=

$1) or completes a PCI

transaction as a master, MARQ is set. If DPCR[MAIE] is set, a master

address interrupt request is generated. MARQ is cleared when the

DSP56300 core writes the DPAR or the PCI bus master enable bit (BM) is

cleared in the CCMR. Hardware, software, personal hardware, and

personal software resets clear MARQ.

Table 6-15. DSP PCI Status Register (DPSR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description