2 bootstrap program, Bootstrap program -5, 2 bootstrap program – Motorola DSP56301 User Manual

Page 79

Bootstrap Program

Core Configuration

4

-5

4.2

Bootstrap Program

In recent revisions of the DSP56301, the bootstrap program is factory-programmed in an

internal 3 K

×

24-bit bootstrap ROM located in program memory space at locations

$FF0000–$FF0BFF.

1

The bootstrap program can load any program RAM segment from an

external byte-wide EPROM, the SCI, Serial EEPROM, other DSP56301, or the host port. The

bootstrap program code for a recent revision of the DSP56301 is listed in Appendix A,

Bootstrap Program.

Upon exiting the reset state, the DSP56301 samples the

MODA

–

MODD

signal lines and loads

their values into OMR[MA–MD]. The mode input signals (

MODA

–

MODD

) and the resulting

MA–MD bits determine which bootstrap mode the DSP56301 enters (see Table 4-1).

D

Host bootstrap 16-bit wide ISA slave glueless interface in UB mode—Loads the program memory

from the Host Interface programmed to operate in the Universal Bus mode supporting ISA (slave)

glueless connection. Using Self-Configuration mode, the base address in the CBMA is initially written with

$2F, which corresponds to an ISA HTXR address of $2FE (Serial Port 2 Modem Status read-only

register). The HI32 bootstrap code expects to read 32 consecutive times the

magic number $0037.

Subsequently, the bootstrap code expects to read a 16-bit word that is the designated ISA Port Address

this address is written into the CBMA. The HOST Processor must poll for the Host Interface to be

reconfigured. This must be done by reading the HSTR and verifying that the value $0013 is read. Then

the host processor starts writing data to the Host Interface. The HI32 bootstrap code expects to read a

24-bit word first that specifies the number of program words, followed by a 24-bit word specifying the

address from which to start loading the program words, followed by a 24-bit word for each program word

to be loaded. The program words are stored in contiguous PRAM memory beginning at the specified

starting address. After reading the program words, program execution starts from the address where

loading started.

Note:

DSP CLKOUT rate must be at least three times the data transfer rate.

E

Host bootstrap 8-bit wide UB mode in double-strobe pin configuration—The hardware reset vector

is located at address $FF0000 in the bootstrap ROM. The program bootstraps through HI32 in UB slave

double-strobe (HWR, HRD) configuration. The DSP56301 is written with 24-bit wide words broken into

8-bit wide host bus transfers. You can use this mode for booting from various microprocessors or

microcontrollers—for example, booting a slave DSP56301 from port A of a master DSP563xx.

Note:

DSP CLKOUT rate must be at least three times the data transfer rate.

F

Host bootstrap 8-bit wide UB mode in single-strobe pin configuration—The hardware reset vector is

located at address $FF0000 in the bootstrap ROM. The program bootstraps through HI32 in UB slave

single-strobe (HRW, HDS) configuration. The DSP56301 is written with 24-bit wide words broken into

8-bit wide host bus transfers. You can use this mode for booting from various microprocessors or

microcontrollers.

Note:

DSP CLKOUT rate must be at least three times the data transfer rate.

1. In early revisions of the DSP56301, the size of the bootstrap program is 192 bytes

×

24 bits.

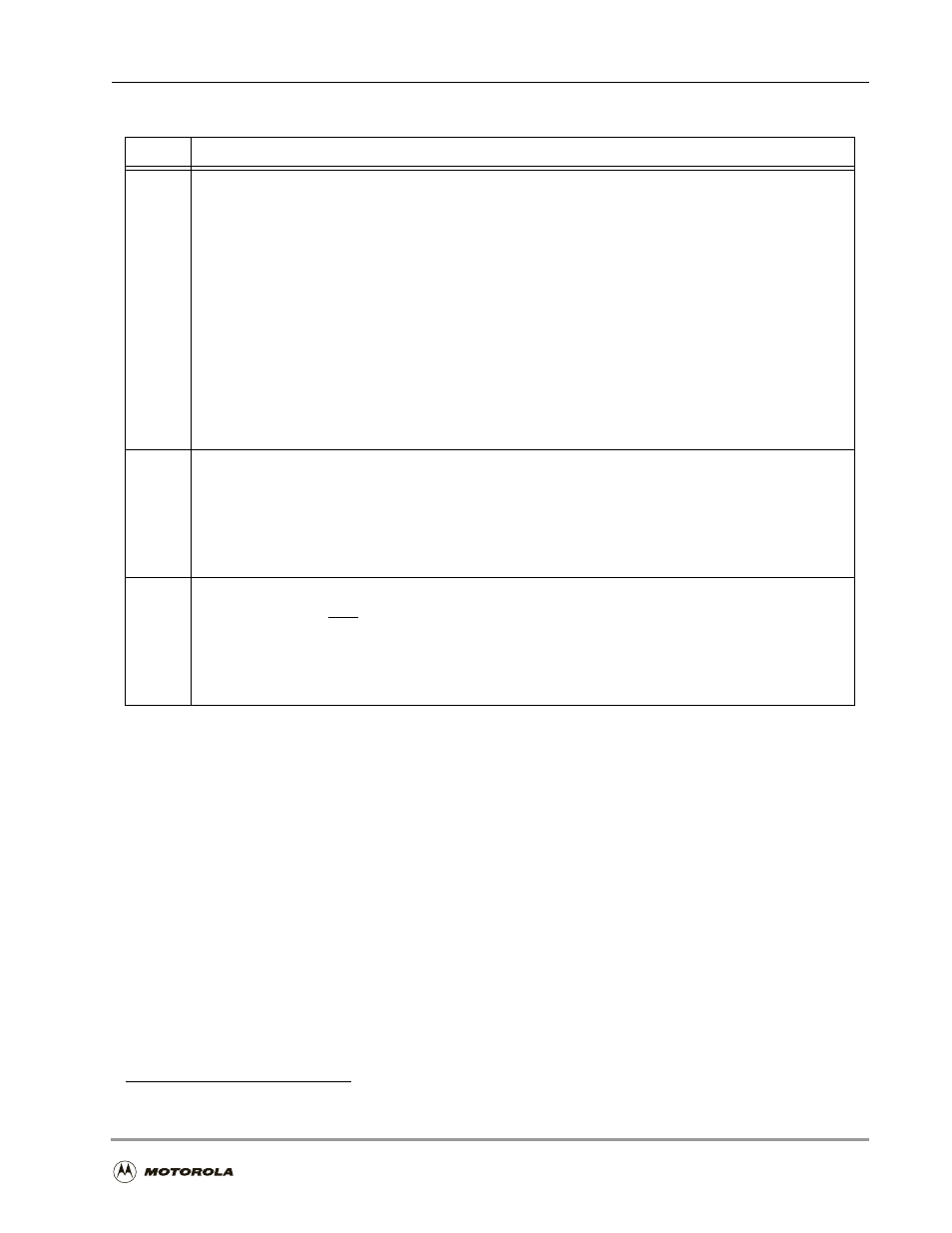

Table 4-2. Operating Mode Definitions (Continued)

Mode

Description