B-24, Figure b-24, Sci clock control registers (sccr) – Motorola DSP56301 User Manual

Page 348: Figure b-24. sci clock control registers (sccr), Application: date: programmer, Reserved, program as 0

Programming Sheets

B

-36

DSP56301 User’s Manual

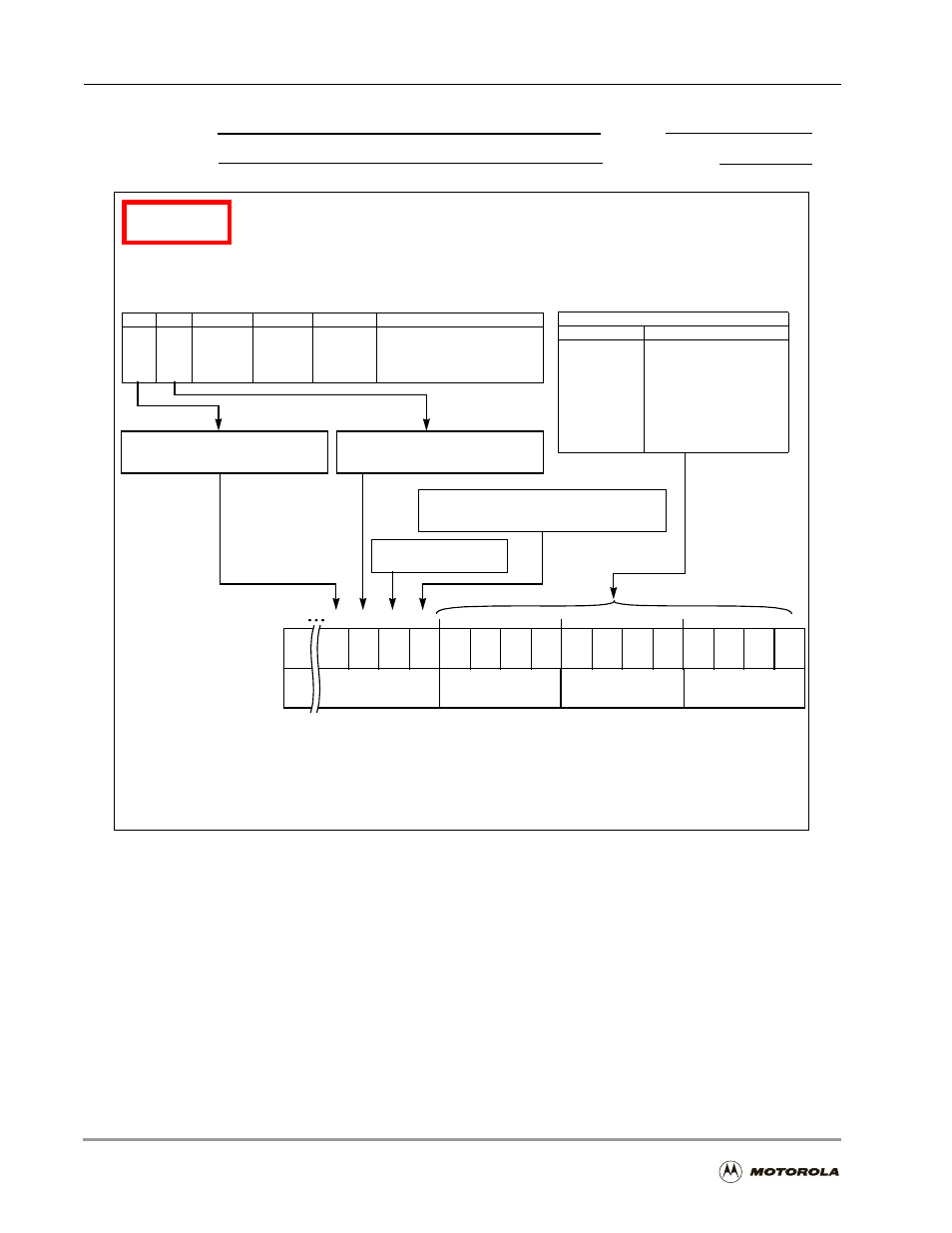

Figure B-24. SCI Clock Control Registers (SCCR)

Application:

Date:

Programmer:

Sheet 2 of 2

SCI

SCI Clock Control Register (SCCR)

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

CD7

CD5

CD4

CD3

CD2

CD1

CD0

23

*

= Reserved, Program as 0

CD6

*

0

TCM RCM

SCP

COD CD11 CD10 CD9

CD8

Clock Divider Bits (CD11–CD0)

CD11–CD0

I

cyc

Rate

$000

I

cyc

/1

$001

I

cyc

/2

$002

I

cyc

/3

•

•

•

•

•

•

$FFE

I

cyc

/4095

$FFF

I

cyc

/4096

SCI Clock Prescaler

0 = ч1 1 = ч 8

Clock Out Divider

0 = Divide clock by 16 before feed to SCLK

1 = Feed clock to directly to SCLK

TCM

RCM

TX Clock

RX Clock

SCLK Pin

Mode

0

0

Internal

Internal

Output

Synchronous/Asynchronous

0

1

Internal

External

Input

Asynchronous only

1

0

External

Internal

Input

Asynchronous only

1

1

External

External

Input

Synchronous/Asynchronous

Receiver Clock Mode/Source

0 = Internal clock for Receiver

1 = External clock from SCLK

Transmitter Clock Mode/Source

0 = Internal clock for Transmitter

1 = External clock from SCLK

Address X:$FFFF9B Read/Write

Reset = $000000