Motorola DSP56301 User Manual

Page 189

Host-Side Programming Model

Host Interface (HI32)

6

-71

6.8.12

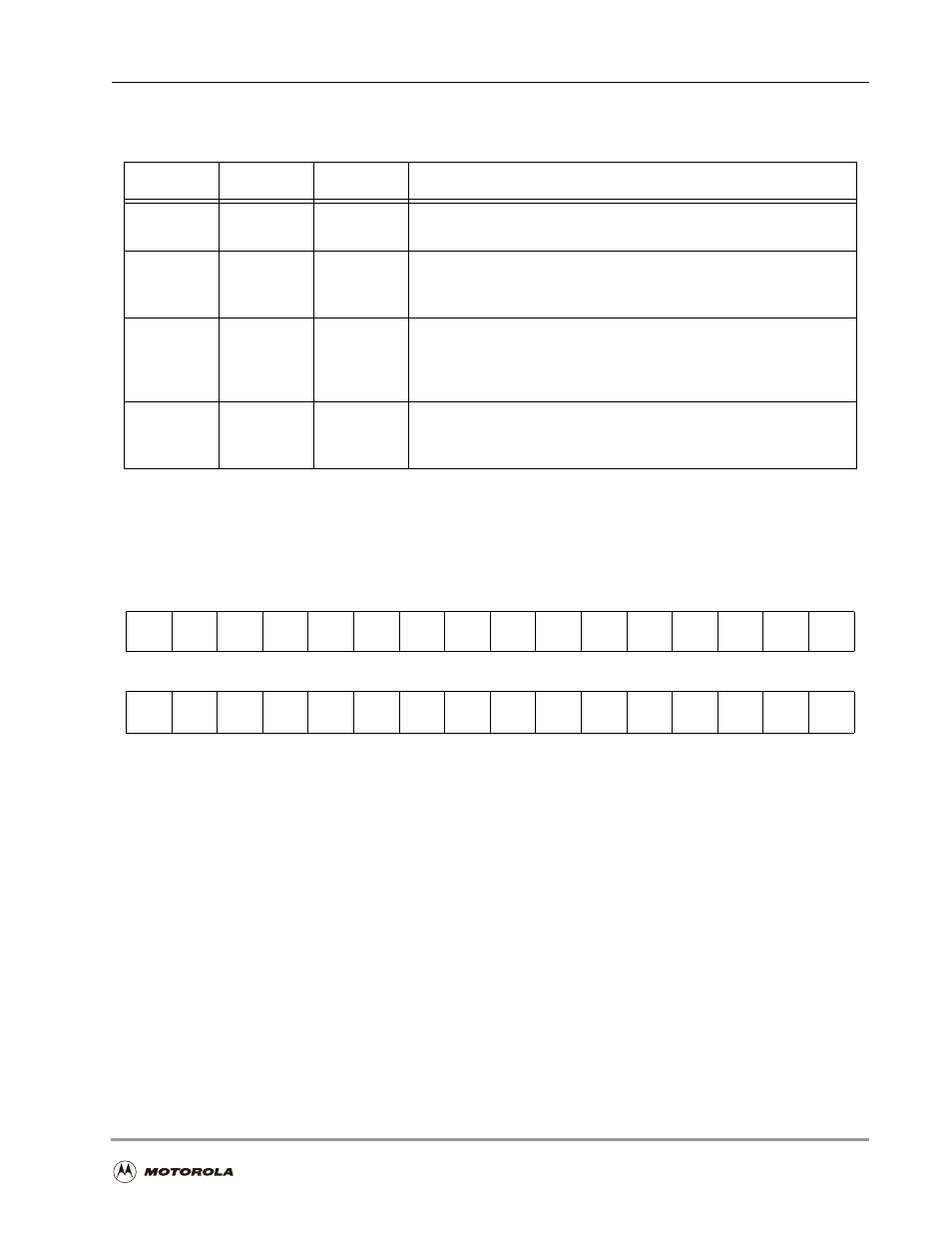

Subsystem ID and Subsystem Vendor ID Configuration Register

(CSID)

r

A PCI-standard read/write register mapped into the PCI configuration space in PCI mode

(HM = $1). The CSID register is read if a configuration read command is in progress and the

PCI address is $2C. In Self-Configuration mode (HM = $5), the DSP56300 core can

indirectly write the CSID (see Section 6.5.5, Self-Configuration Mode (DCTR[HM] = $5),

on page 6-16).

The host cannot access the CSID register when the system is not in PCI mode (HM

≠

$1

)

. This

register uniquely identifies the add-in board or subsystem in which the DSP56301 resides.

Add-in card vendors can use this mechanism to distinguish their cards from one another even

though the cards may have the same DSP56301 on them (and therefore the same Vendor ID

and Device ID). Implementation of this register is optional, and an all-zero value indicates

that the device (for example, add-in board) does not support subsystem identification. The

CSID bits are cleared after power-up. Any reset does not affect the value written to the CSID.

15–4

PM[15–4]

0

Memory Base Address Low (Hardwired to zeros)

3

PF

0 (Hardwired) Pre-Fetch (Hardwired to zero)

Indicates whether the data is pre-fetchable. PF is hardwired to zero and

is unaffected by any type of reset.

2–1

MS[1 –0]

0 (Hardwired) Memory Space (Hardwired to zeros)

Specifies that the CBMA register is 32 bits wide and mapping can be

done anywhere in the 32-bit memory space. MS1 and MS0 are

hardwired to zero and are unaffected by any type of reset.

0

MSI

0 (Hardwired) Memory Space Indicator (Hardwired to zero)

Specifies that the CBMA register maps the HI32 into the PCI memory

space. MSI is hardwired to zero and is unaffected by any type of reset.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

SID15 SID14 SID13 SID12 SID11 SID10 SID9

SID8

SID7

SID6

SID5

SID4

SID3

SID2

SID1

SID0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SVID

15

SVID

14

SVID

13

SVID

12

SVID

11

SVID

10

SVID

9

SVID

8

SVID

7

SVID

6

SVID

5

SVID

4

SVID

3

SVID

2

SVID

1

SVID

0

Figure 6-21. Subsystem ID and Subsystem Vendor ID Configuration

Register (CSID)

Table 6-29. Memory Space Base Address Configuration Register (CBMA)

Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description