7 dma control registers 5–0 (dcr[5–0]), Dma control registers 5–0 (dcr[5–0]) -29, Dma control register (dcr) -29 – Motorola DSP56301 User Manual

Page 103: Dma control register (dcr) bit definitions -29, Figure 4-9. dma control register (dcr)

DMA Control Registers 5–0 (DCR[5–0])

Core Configuration

4

-29

4.7

DMA Control Registers 5–0 (DCR[5–0])

The DMA Control Registers (DCR[5–0]) are read/write registers that control the DMA

operation for each of their respective channels. All DCR bits are cleared during processor

reset.

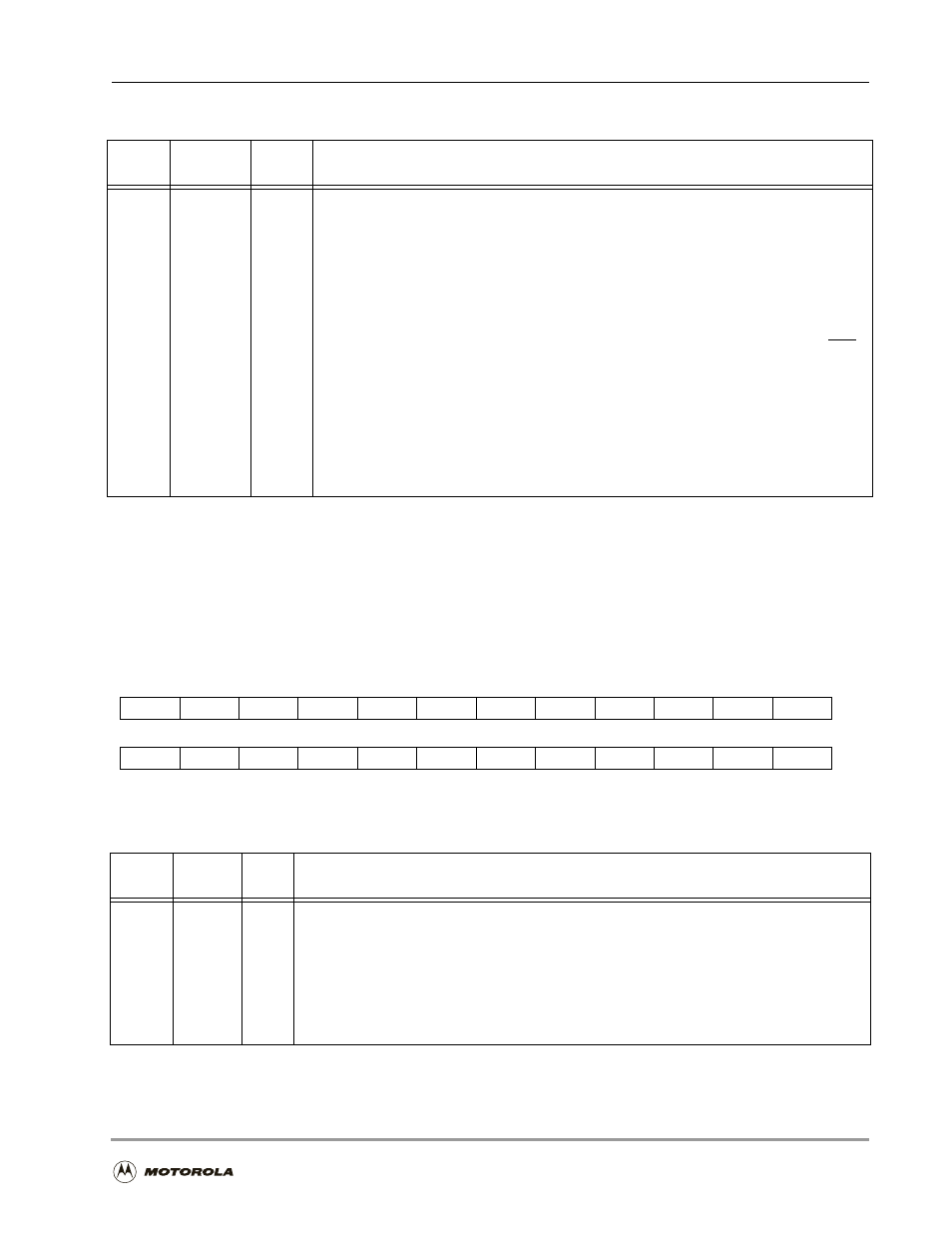

Figure 4-9. DMA Control Register (DCR)

1–0

BAT[1–0]

0

Bus Access Type

Read/write bits that define the type of external memory (DRAM or SRAM) to access for

the area defined by the BAC[11–0],BYEN, BXEN, and BPEN bits. The encoding of

BAT[1–0] is:

n

00 = Reserved

n

01 = SRAM access

n

10 = DRAM access

n

11 = Reserved

When the external access type is defined as a DRAM access (BAT[1–0] = 10), AA/RAS

acts as a Row Address Strobe (RAS) signal. Otherwise, it acts as an Address Attribute

signal. External accesses to the default area always execute as if BAT[1–0] = 01 (that is,

SRAM access). If Port A is used for external accesses, the BAT bits in the AAR3–0

registers must be initialized to the SRAM access type (that is, BAT = 01) or to the DRAM

access type (that is BAT = 10). To ensure proper operation of Port A, this initialization

must occur even for an AAR register that is not used during any Port A access.

Note:

At reset, the BAT bits are initialized to 00.

Table 4-12. DMA Control Register (DCR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Description

23 DE

0

DMA Channel Enable

Enables the channel operation. Setting DE either triggers a single block DMA transfer in the

DMA transfer mode that uses DE as a trigger or enables a single-block, single-line, or

single-word DMA transfer in the transfer modes that use a requesting device as a trigger. DE

is cleared by the end of DMA transfer in some of the transfer modes defined by the DTM bits.

If software explicitly clears DE during a DMA operation, the channel operation stops only

after the current DMA transfer completes (that is, the current word is stored into the

destination).

Table 4-11. Address Attribute Registers (AAR[0–3]) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description

23

22

21

20

19

18

17

16

15

14

13

12

DE

DIE

DTM2

DTM1

DTM0

DPR1

DPR0

DCON

DRS4

DRS3

DRS2

DRS1

11

10

9

8

7

6

5

4

3

2

1

0

DRS0

D3D

DAM5

DAM4

DAM3

DAM2

DAM1

DAM0

DDS1

DDS0

DSS1

DSS0