3 timer toggle (mode 2), Timer toggle (mode 2) -10, Toggle mode, trm = 1 -10 – Motorola DSP56301 User Manual

Page 272: Figure 9-7. toggle mode, trm = 1

Operating Modes

9

-10

DSP56301 User’s Manual

9.3.1.3 Timer Toggle (Mode 2)

In Mode 2, the timer periodically toggles the polarity of the TIO signal. When the timer is

enabled, the TIO signal is loaded with the value of the TCSR[INV] bit. When the counter

value matches the value in the TCPR, the polarity of the TIO output signal is inverted.

TCSR[TCF] is set, and a compare interrupt is generated if the TCSR[TCIE] bit is set. If the

TCSR[TRM] bit is set, the counter is loaded with the value of the TLR when the next timer

clock is received, and the count resumes. If the TRM bit is cleared, the counter continues to

increment on each timer clock. This process repeats until the timer is cleared (disabling the

timer). The TCPR[TLR] value sets the delay between starting the timer and toggling the TIO

signal. To generate output signals with a delay of X clock cycles between toggles, set the TLR

value to X/2, and set the TCSR[TRM] bit. This process repeats until the timer is disabled (that

is, TCSR[TE] is cleared).

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Name

Function

TIO

Clock

0

0

1

0

2

Toggle

Timer

Output

Internal

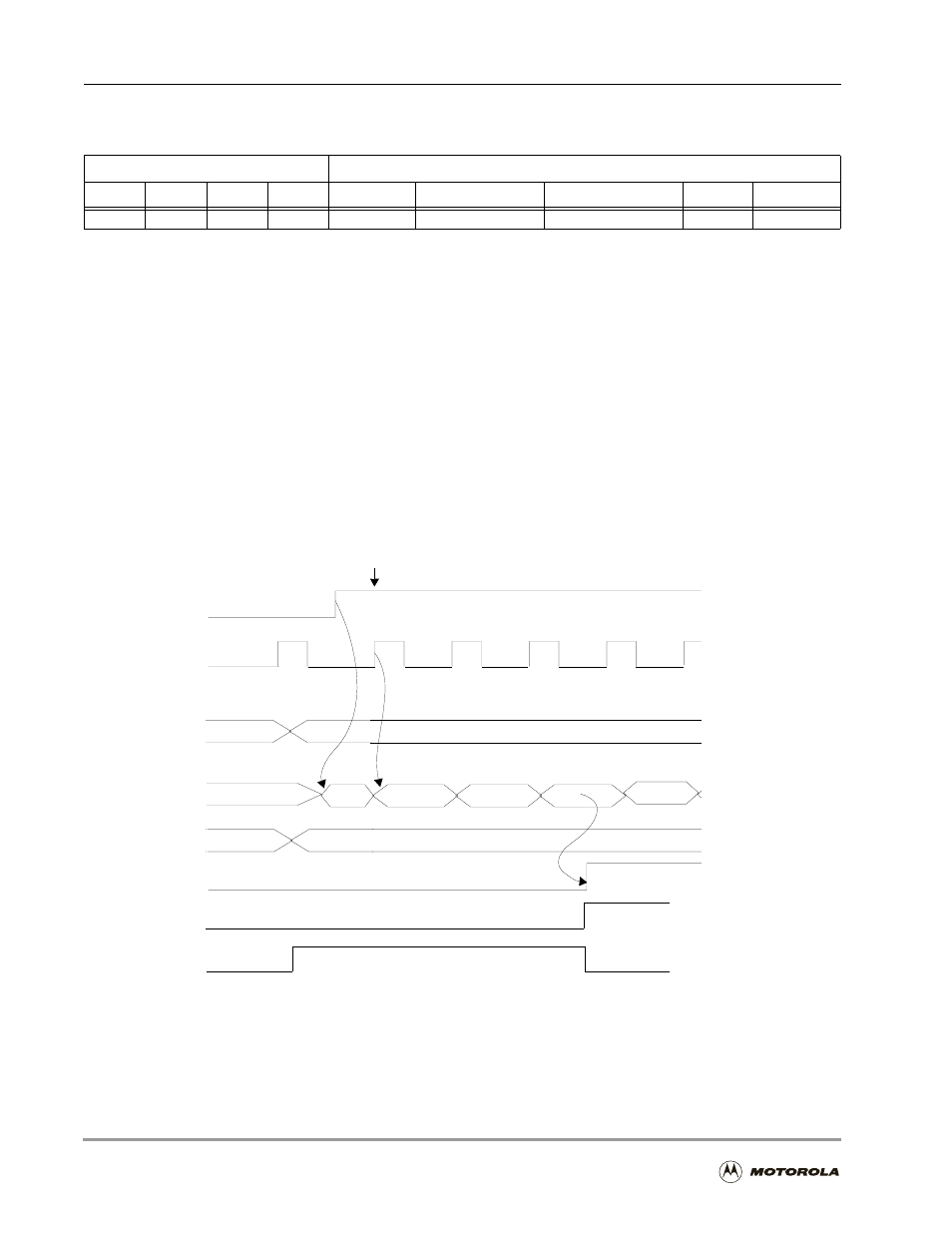

Figure 9-7. Toggle Mode, TRM = 1

Mode 2 (internal clock): TRM = 1

N = write preload

M = write compare

TE

Clock

(CLK/2 or prescale CLK)

TLR

TCPR

TCF (Compare Interrupt if TCIE = 1)

Counter (TCR)

first event

M

0

N

N + 1

M

N

N + 1

N

pulse width =

M - N clock

periods

TIO pin (INV = 0)

TIO pin (INV = 1)