Motorola DSP56301 User Manual

Page 87

Central Processor Unit (CPU) Registers

Core Configuration

4

-13

18

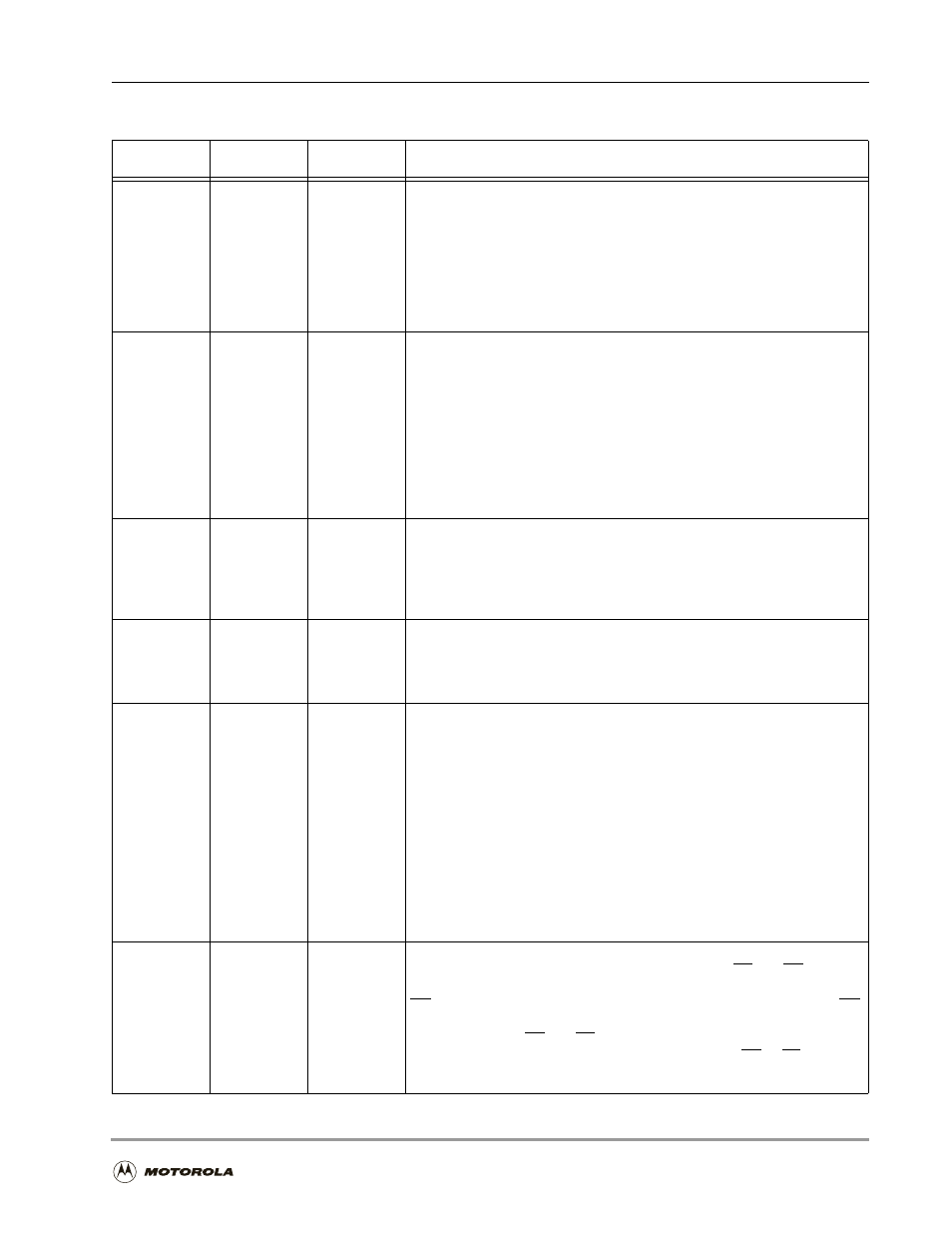

EOV

0

Stack Extension Overflow Flag

Set when a stack overflow occurs in Stack Extended mode. Extended

stack overflow is recognized when a push operation is requested while SP

= SZ (Stack Size register), and the Extended mode is enabled by the SEN

bit. The EOV flag is a

sticky bit (that is, cleared only by hardware reset or

by an explicit MOVEC operation to the OMR). The transition of the EOV

flag from zero to one causes a Priority Level 3 (Non-maskable) stack error

exception.

17

EUN

0

Stack Extension Underflow Flag

Set when a stack underflow occurs in Extended Stack mode. Extended

stack underflow is recognized when a pull operation is requested, SP = 0,

and the SEN bit enables Extended mode. The EUN flag is a

sticky bit (that

is, cleared only by hardware reset or by an explicit MOVEC operation to

the OMR). Transition of the EUN flag from zero to one causes a Priority

Level 3 (Non-maskable) stack error exception.

Note:

While the chip is in Extended Stack mode, the UF bit in the SP

acts like a normal counter bit.

16

XYS

0

Stack Extension XY Select

Determines whether the stack extension is mapped onto X or Y memory

space. If the bit is clear, then the stack extension is mapped onto the X

memory space. If the XYS bit is set, the stack extension is mapped to the

Y memory space.

15

ATE

0

Address Trace Enable

When set, the Address Trace Enable (ATE) bit enables Address Trace

mode. The Address Trace mode is a debugging tool that reflects internal

memory accesses at the external bus address.

14

APD

0

Address Attribute Priority Disable

Disables the priority assigned to the Address Attribute signals (AA[0–3]).

When APD = 0 (default setting), the four Address Attribute signals each

have a certain priority: AA3 has the highest priority, AA0 has the lowest

priority. Therefore, only one AA signal can be active at one time. This

allows continuous partitioning of external memory; however, certain

functions, such as using the AA signals as additional address lines,

require the use of additional interface hardware. When APD is set, the

priority mechanism is disabled, allowing more than one AA signal to be

active simultaneously. Therefore, the AA signals can be used as

additional address lines without the need for additional interface

hardware. For details on the Address Attribute Registers, see Section

4.6.3,

Address Attribute Registers (AAR[0–3]), on page 4-27.

13

ABE

0

Asynchronous Bus Arbitration Enable

Eliminates the setup and hold time requirements for BB and BG, and

substitutes a required non-overlap interval between the deassertion of one

BG input to a DSP56300 family device and the assertion of a second BG

input to a second DSP56300 family device on the same bus. When the

ABE bit is set, the BG and BB inputs are synchronized. This

synchronization causes a delay between a change in BG or BB until this

change is actually accepted by the receiving device.

Table 4-4. Operating Mode Register (OMR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description