1 sci control register (scr), Sci control register (scr) -12, Sci control register (scr) bit definitions -12 – Motorola DSP56301 User Manual

Page 248: Figure 8-3, 1 sci control register (scr)

SCI Programming Model

8

-12

DSP56301 User’s Manual

8.6.1

SCI Control Register (SCR)

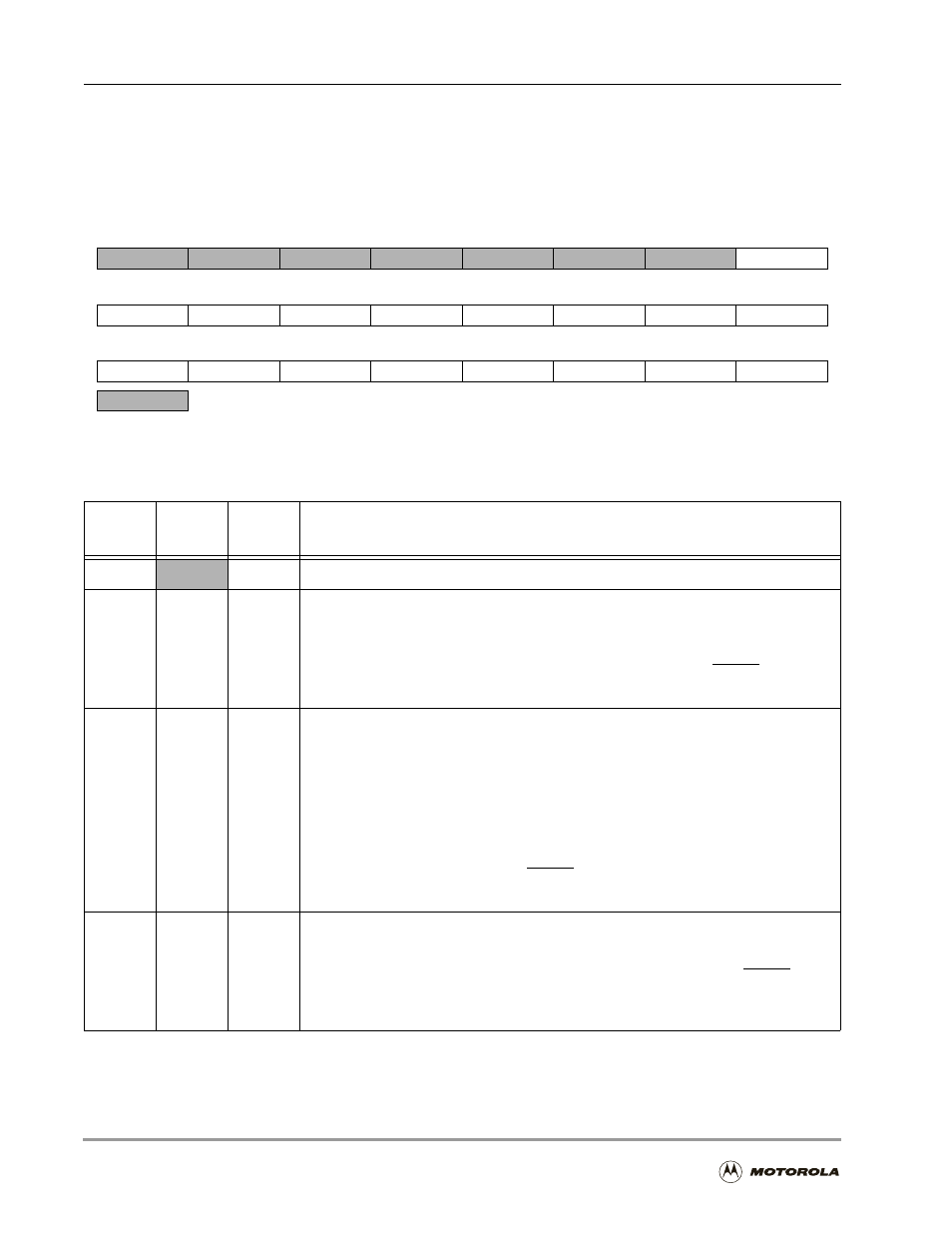

The SCR is a read/write register that controls the serial interface operation. Seventeen of its

24 bits are defined.

.

23

22

21

20

19

18

17

16

REIE

15

14

13

12

11

10

9

8

SCKP

STIR

TMIE

TIE

RIE

ILIE

TE

RE

7

6

5

4

3

2

1

0

WOMS

RWU

WAKE

SBK

SSFTD

WDS2

WDS1

WDS0

—Reserved bit; read as 0; write to 0 for future compatibility.

Figure 8-3. SCI Control Register (SCR)

Table 8-2. SCI Control Register (SCR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Description

23–17

0

Reserved. Write to 0 for future compatibility.

16

REIE

0

Receive with Exception Interrupt Enable

Enables/disables the SCI receive data with exception interrupt. If REIE is cleared, the

receive data with exception interrupt is disabled. If both REIE and RDRF are set, and

PE, FE, and OR are not all cleared, the SCI requests an SCI receive data with

exception interrupt from the interrupt controller. Either a hardware RESET signal or a

software RESET instruction clears REIE.

15

SCKP

0

SCI Clock Polarity

Controls the clock polarity sourced or received on the clock signal (SCLK), eliminating

the need for an external inverter. When SCKP is cleared, the clock polarity is positive;

when SCKP is set, the clock polarity is negative. In Synchronous mode, positive

polarity means that the clock is normally positive and transitions negative during valid

data. Negative polarity means that the clock is normally negative and transitions

positive during valid data. In Asynchronous mode, positive polarity means that the

rising edge of the clock occurs in the center of the period that data is valid. Negative

polarity means that the falling edge of the clock occurs during the center of the period

that data is valid. Either a hardware RESET signal or a software RESET instruction

clears SCKP.

14

STIR

0

Timer Interrupt Rate

Controls a divide-by-32 in the SCI Timer interrupt generator. When STIR is cleared, the

divide-by-32 is inserted in the chain. When STIR is set, the divide-by-32 is bypassed,

thereby increasing timer resolution by a factor of 32. Either a hardware RESET signal

or a software RESET instruction clears this bit. To ensure proper operation of the timer,

STIR must not be changed during timer operation (that is, if TMIE = 1).