Motorola DSP56301 User Manual

Page 106

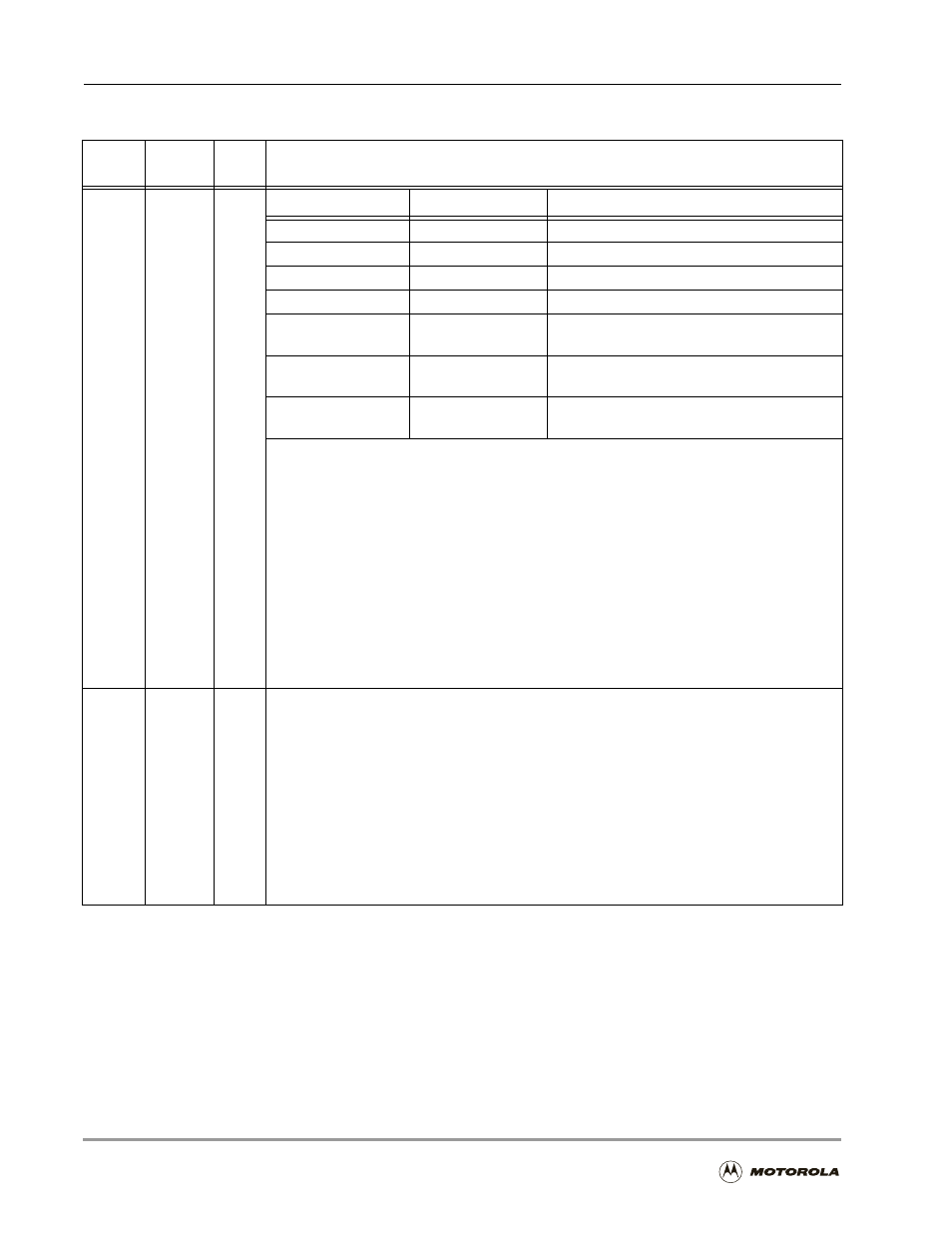

DMA Control Registers 5–0 (DCR[5–0])

4

-32

DSP56301 User’s Manual

18–17

cont.

DPR[1–0]

OMR - CDP[1–0]

CP[1–0]

Core Priority

00

00

0 (lowest)

00

01

1

00

10

2

00

11

3 (highest)

01

xx

DMA accesses have higher priority than core

accesses

10

xx

DMA accesses have the same priority as core

accesses

11

xx

DMA accesses have lower priority than core

accesses

n

If DMA priority > core priority (for example, if CDP = 01, or CDP = 00 and

DPR > CP), the DMA performs the external bus access first and the core waits for the

DMA channel to complete the current transfer.

n

If DMA priority = core priority (for example, if CDP = 10, or CDP = 00 and

DPR = CP), the core performs all its external accesses first and then the DMA channel

performs its access.

n

If DMA priority < core priority (for example, if CDP=11, or CDP = 00 and

DPR < CP), the core performs its external accesses and the DMA waits for a free slot

in which the core does not require the external bus.

n

In Dynamic Priority mode (CDP = 00), the DMA channel can be halted before

executing both the source and destination accesses if the core has higher priority. If

another higher-priority DMA channel requests access, the halted channel finishes its

previous access with a new higher priority before the new requesting DMA channel is

serviced.

16

DCON

0

DMA Continuous Mode Enable

Enables/disables DMA Continuous mode. When DCON is set, the channel enters the

Continuous Transfer mode and cannot be interrupted during a transfer by any other DMA

channel of equal priority. DMA transfers in the continuous mode of operation can be

interrupted if a DMA channel of higher priority is enabled after the continuous mode transfer

starts. If the priority of the DMA transfer in continuous mode

(that is, DCON = 1) is higher

than the core priority (CDP = 01, or CDP = 00 and DPR > CP), and if the DMA requires an

external access, the DMA gets the external bus and the core is not able to use the external

bus in the next cycle after the DMA access even if the DMA does not need the bus in this

cycle. However, if a refresh cycle from the DRAM controller is requested, the refresh cycle

interrupts the DMA transfer. When DCON is cleared, the priority algorithm operates as for the

DPR bits.

Table 4-12. DMA Control Register (DCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description