Hi32 features, core-side and host-side -2, Table 6-1. hi32 features, core-side and host-side – Motorola DSP56301 User Manual

Page 120

Features

6

-2

DSP56301 User’s Manual

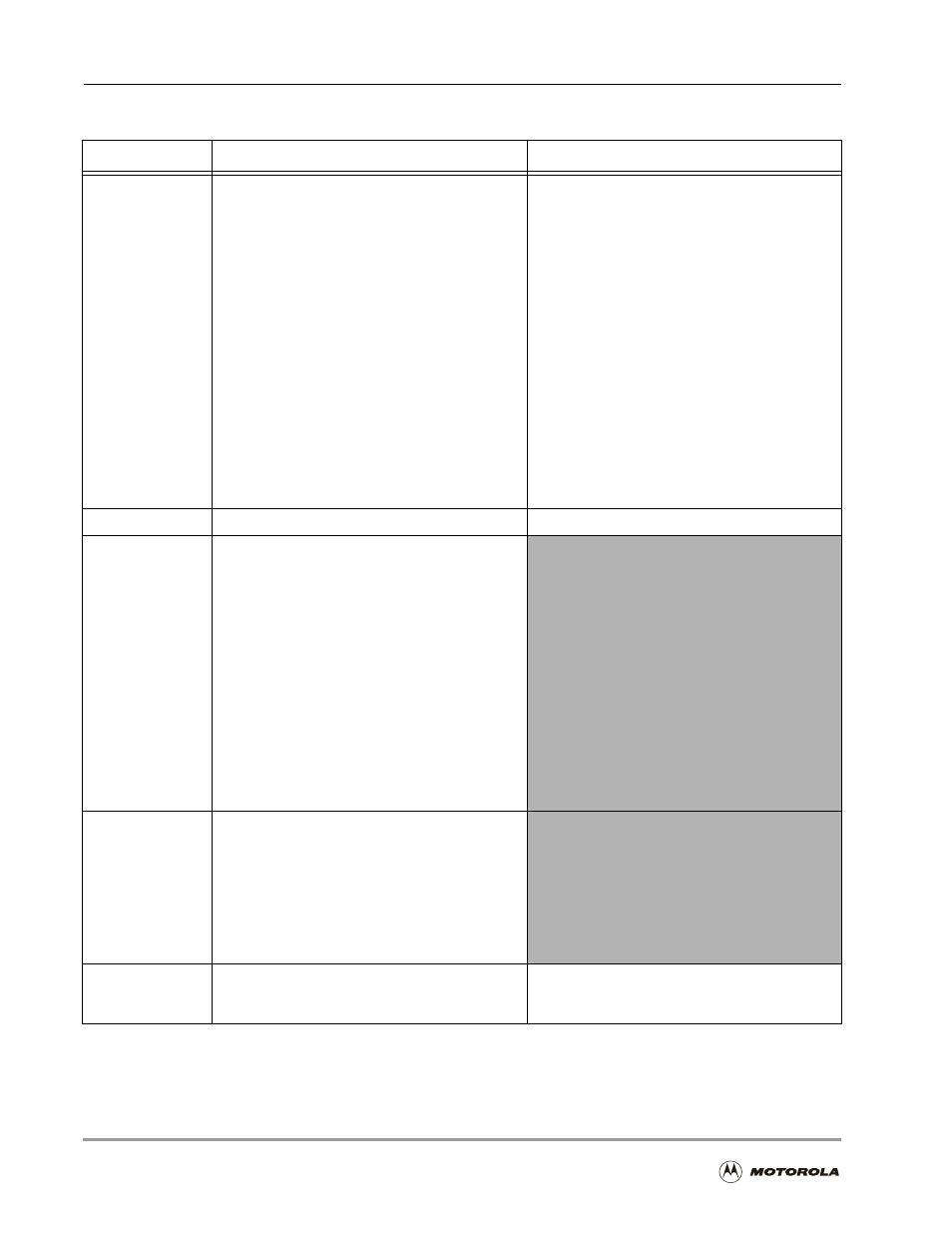

Table 6-1. HI32 Features, Core-Side and Host-Side

Feature

Core-Side Interface

Host-Side Interface

Mapping

11 internal I/O space locations

PCI mode: Memory space:16 K Dword (32-bit

wide) locations composed of:

n

Three 32-bit read/write registers

(control, status, and host command)

n

16377 32-bit read/write locations

corresponding to one 32-bit input data

FIFO and one 32-bit output data FIFO

n

Four 32-bit reserved locations (read only)

n

Configuration space:Sixty-four 32-bit

locations (57 of which are reserved)

Universal Bus mode:

n

Three 24-bit read/write registers

(control, status and host command)

n

One 24-bit read/write register for input

and output data FIFO (four of which are

reserved)

n

Eight locations up to 24-bits wide (four are

reserved)

Word Size

24 bits

8, 16, 24, or 32 bits

PCI Mode: Data

Format

Conversion

Output data alignment of 16 bit words to 16-bit

double words (Dwords)

Output data alignment of 24-bit words to 32-bit

Dwords

n

Left aligned and zero filled

n

Right aligned and zero extended

n

Right aligned and sign extended

Input data alignment of 32-bit Dwords to 24-bit

words

(three MSBs, three LSBs)

True 32-bit input and output data transfers

32-bit PCI bus data to two DSP56300 core 16-bit

words, and

vice versa

Universal Bus

Mode: Data

Format

Conversion

Output data alignment of 24-bit words to 16-bit

words (two MSBs, two LSBs)

Input data alignment of 16-bit words to 24-bit

words

n

left aligned and zero filled

n

right aligned and zero extended

n

right aligned and sign extended

Data Buffers

FIFOs up to eight words deep on both transmit

and receive data paths

FIFOs six or eight words deep on transmit and

receive data paths, five deep in Universal Bus

mode