B-11, Figure b-11, Dsp pci control register (dpcr) – Motorola DSP56301 User Manual

Page 335: Host processor (hi32)

Programming Sheets

Programming Reference

B

-23

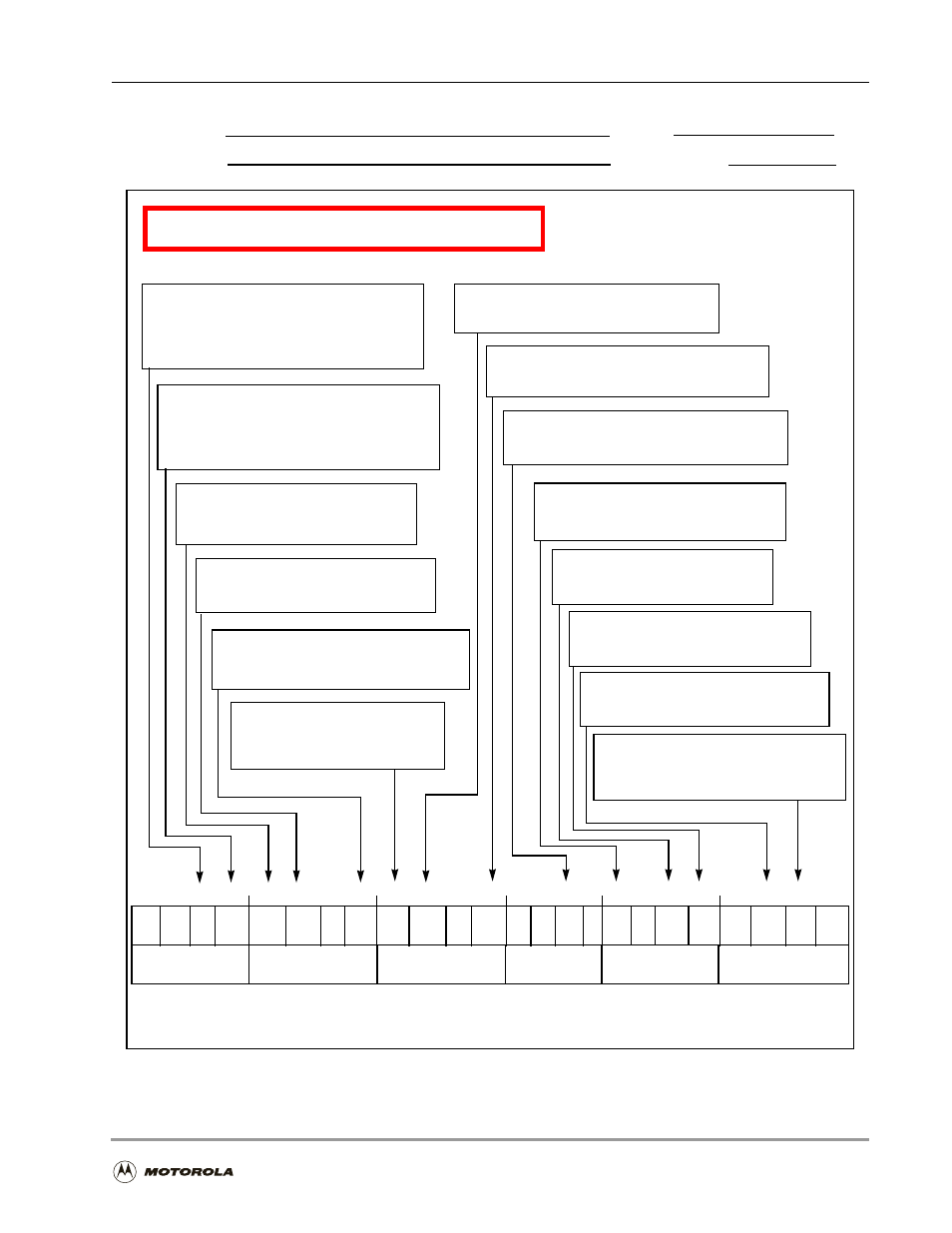

Figure B-11. DSP PCI Control Register (DPCR)

Host Processor (HI32)

DSP PCI Control Register (DPCR)

Reset = $000000

15 14

13

12 11 10 9

8

7

6

5

4

3

2

1

0

PEIE

MRIE

MTIE

19 18

17

16

23 22 21 20

CLRT

MWSD MACE

RBLE

IAE

Master Transmit Interrupt Enable, Bit 1

Receive Buffer Lock Enable, Bit 20

0 = HDTC bit not set. PCI write access to HTXR

cannot occur.

MAIE

Master Receive Interrupt Enable, Bit 2

0 =

Disables master receive interrupts.

1 =

Enables master receive interrupts.

1 = HDTC bit is set. PCI write access to HTXR

*

= Reserved, Program as 0

*

0

*

0

*

0

*

0

*

0

SERF MTT

Master Wait State Disable, Bit 19

0 = Enables insertion of PCI wait states.

1 = Disables insertion of PCI wait states.

Master Access Counter Enable, Bit 18

0 = Disables master access counter.

1 = Enables master access counter.

0 =

Disables master transmit interrupts.

1 =

Enables master transmit interrupts.

0 = Disables transfer complete interrupt requests.

1 = Enables transfer complete interrupt requests.

Transfer Complete Interrupt Enable, Bit 12

0 = HI32 hardware controls the HSERR pin.

1 = Pulse HSERR pin one PCI clock cycle.

System Error Force, Bit 16

0 = PCI bus is in idle state.

1 = Generates master-initiated

Master Transfer Terminate, Bit 15

*

0

*

0

TCIE

TTIE

*

0

TAIE

*

0

*

0

Insert Address Enable, Bit 21

0 = Does not write PCI transaction address.

(Ignored when HI32 is not in PCI mode. Can be

1 = Writes PCI transaction address to HTXR.

set only when DPCR[RBLE]] = 1.)

0 = No data transaction pending.

1 = Clears HI32 master-to-host bus data path.

Clear Transmitter, Bit 14

can occur.

Note: All bits work only in PCI mode (DCTR[HM] = $1).

Address: X:FFFFC6 Read/Write

Application:

Date:

Programmer:

Sheet 2 of 10

transaction termination

Master Address Interrupt Enable, Bit 4

0 = Disables master address interrupts.

1 = Enables master address interrupts.

0 = Disables parity error interrupts.

1 = Enables parity error interrupts.

Parity Error Interrupt Enable, Bit 5

0 = Disables transaction abort interrupts.

1 = Enables transaction abort interrupts.

Transaction Abort Interrupt Enable, Bit 7

0 = Disables transaction interrupt requests.

1 = Enables transaction interrupt requests.

Transaction Termination Interrupt Enable, Bit 9