Motorola DSP56301 User Manual

Page 187

Host-Side Programming Model

Host Interface (HI32)

6

-69

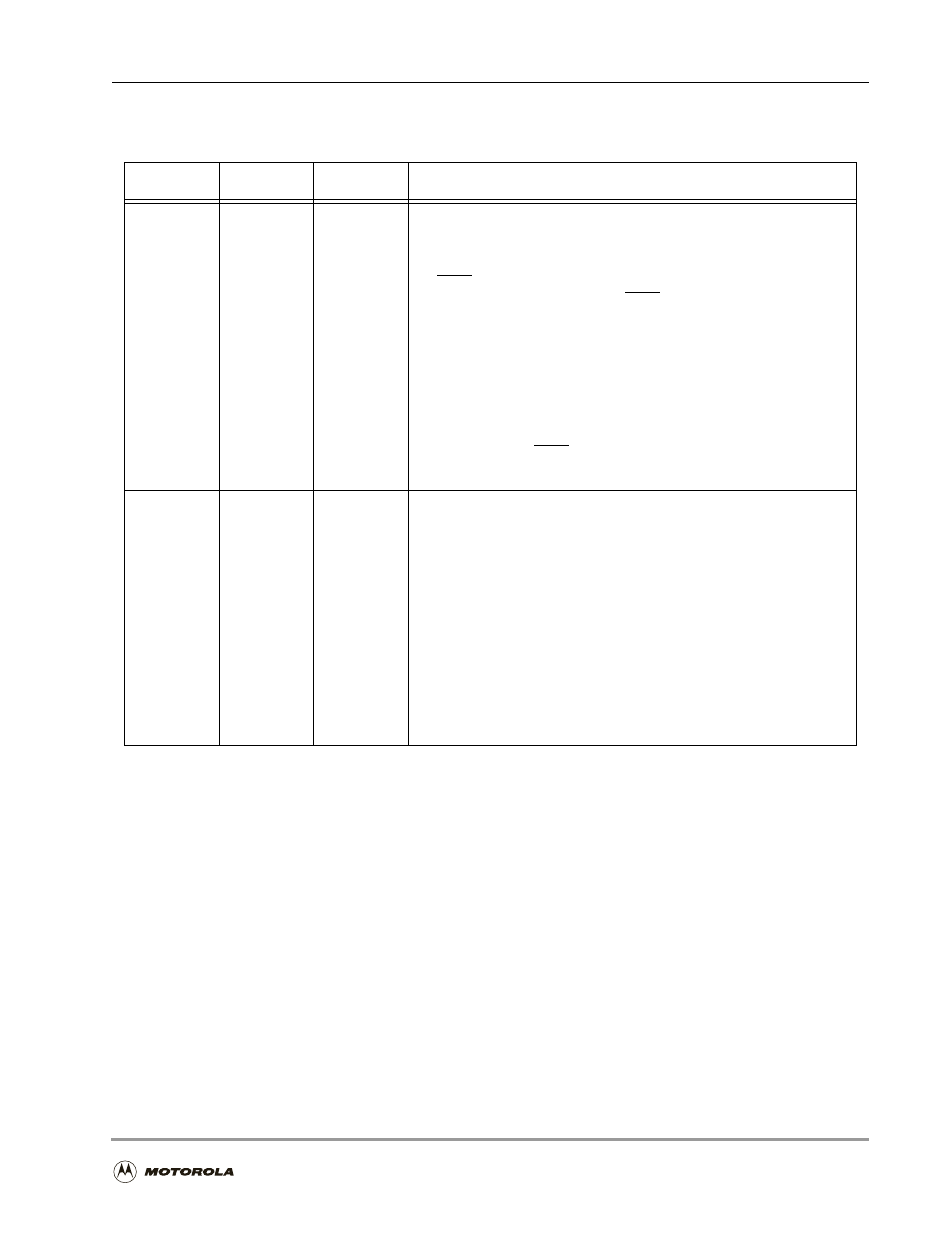

15–8

LT[7–0]

0

Latency Timer (High)

In PCI mode (HM = $1), specify the value of the latency timer for this

PCI bus master in units of PCI bus clock cycles. In the Universal Bus

modes (HM = $2,$3) with HIRH cleared, LT[7–0] specify the duration of

the HIRQ pulse in units of DSP56300 core clock cycles. The following

equation gives the duration of the HIRQ pulse:

HIRQ_PULSE_WIDTH = (LT[7–0]_Value + 1) •

DSP56300_Core_clock_cycle

The DSP56300 core can write to these bits in Self-Configuration mode

(see Example 6-4 on page 6-17). The personal hardware reset clears

LT[7–0].

Note:

When the HIRQ pin is used in pulse mode (HIRH = 0 in

DCTR), the LT[7–0] value (in CLAT) should not be zero.

7–0

CLS[7–0]

0

Cache Line Size

Read/write bits that specify the system cache line size in units of 32-bit

words. These bits compose the Cache Line Size Configuration Register

(CCLS).

Note:

When some PCI commands are used (for example, the

Memory Write and Invalidate commands), a minimum transfer

of one complete cache line should be guaranteed. This should

be reflected by the Burst Length value used (BL[5–0]) in the

DMPC. The cache line size is set by the PCI configurator in

the Cache Line Size Configuration Register (CCLS), but the

DSP56300 core cannot read this value. The system should

provide the CCLS value to the DSP56300 core in another

user-defined way.

Table 6-28. Header Type/Latency Timer Configuration Register (CHTY/CLAT/CCLS)

Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description