Figure b-2, Operating mode register (omr), Central processor – Motorola DSP56301 User Manual

Page 326: Figure b-2. operating mode register (omr)

Programming Sheets

B

-14

DSP56301 User’s Manual

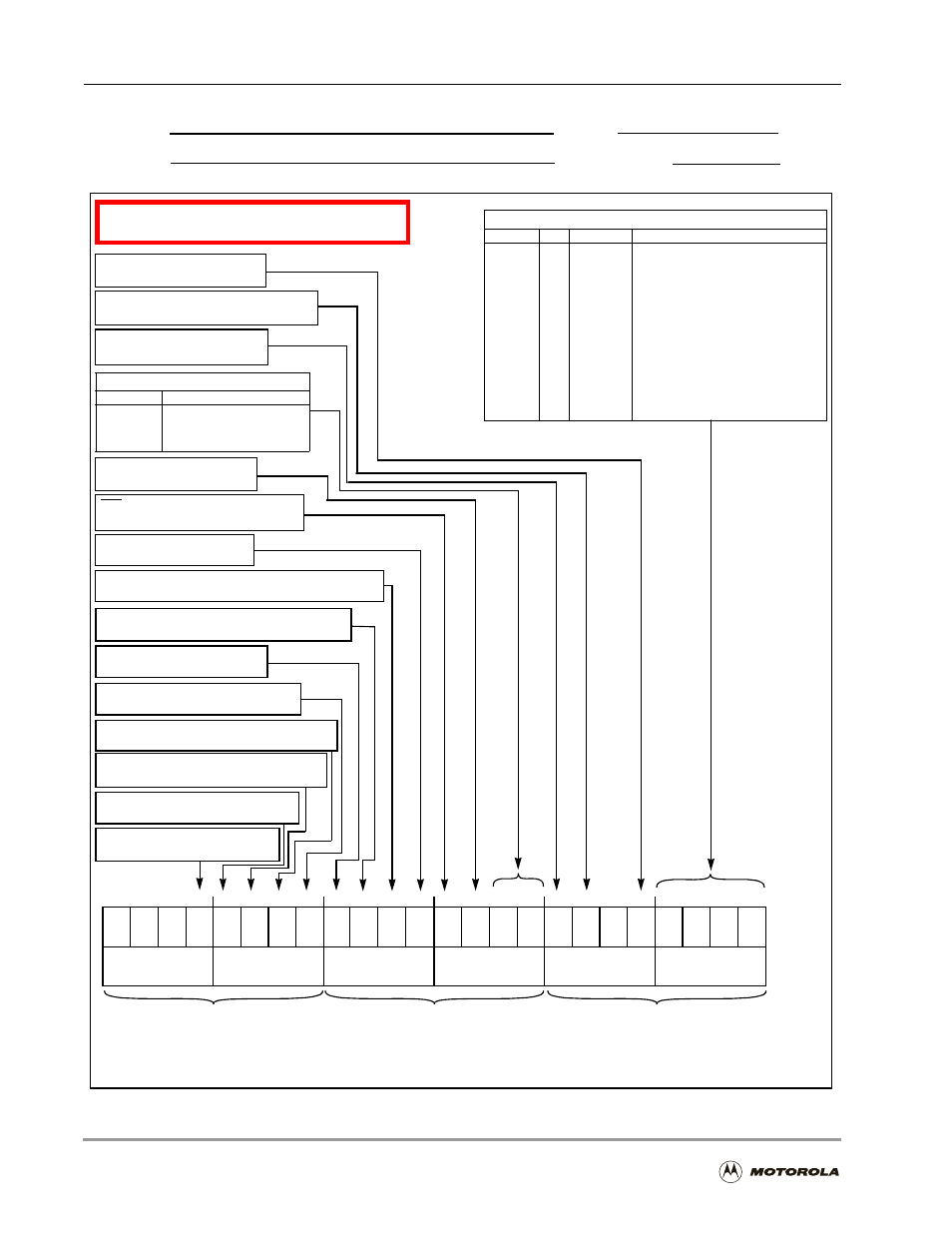

Figure B-2. Operating Mode Register (OMR)

Chip Operating Modes

MOD(D:A)

Mode Reset Vector

Description

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

$C00000

$FF0000

$FF0000

—

$FF0000

$FF0000

$FF0000

$FF0000

$008000

$FF0000

$FF0000

$FF0000

$FF0000

$FF0000

$FF0000

$FF0000

Expanded mode

Bootstrap from byte-wide memory

Bootstrap through SCI

Reserved

Bootstrap from ISA host

Bootstrap from HC11 host

Bootstrap from 8051 host

Bootstrap from MC68302 host

Expanded mode

Bootstrap from byte-wide memory

Bootstrap through SCI

Bootstrap through SCI

Bootstrap from ISA host

Bootstrap from HC11 host

Bootstrap from 8051 host

Bootstrap from MC68302 host

Application:

Date:

Programmer:

Sheet 2 of 2

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

EBD

MC

MB

MA

19 18 17 16

23 22 21 20

SD

BRT

TAS

SEN

CDP1 CDP0

WRP EOV EUN

XYS

BE

MD

Core-DMA Priority

CDP(1:0)

Core-DMA Priority

00

01

10

11

Core vs DMA Priority

DMA accesses > Core

DMA accesses = Core

DMA accesses < Core

*

0

*

0

*

0

*

0

Chip Operating Mode

Register (COM)

System Stack Control

Status Register (SCS)

Extended Chip Operating

Mode Register (EOM)

Operating Mode Register (OMR)

Read/Write

Reset = $00030X; X

= latched from levels on Mode pins

Central Processor

*

= Reserved, Program as 0

Burst Mode Enable

TA Synchronize Select

Address Trace Enable

Stack Extension XY Select

Extended Stack Underflow Flag

Extended Stack Overflow Flag

Extended Stack Wrap Flag

Memory Switch Mode

MS

External Bus Disable

Stop Delay

ATE APD

ABE

Address Attribute Priority Disable

Asynchronous Bus Arbitration Enable

Bus Release Timing

0 = enable 1 = disable

0 = 128 K clocks 1 = 16 clocks

0 = disable 1 = enable

0 = disable 1 = enable

0 = not selected 1 = selected

0 = fast 1 = slow

0 = disable 1 = enable

0 = no wrap 1 = wrap (sticky bit)

0 = enable 1 = disable

0 = disable 1 = enable

0 = no 1 = overflow

0 = no 1 = underflow

0 = X memory 1 = Y memory

Stack Extension Enable

0 = disable 1 = enable