Figure b-9, Dma control registers 5–0 (dcr[5–0]), Programming sheets – Motorola DSP56301 User Manual

Page 333: B-21, Application: date: programmer, Programming reference

Programming Sheets

Programming Reference

B

-21

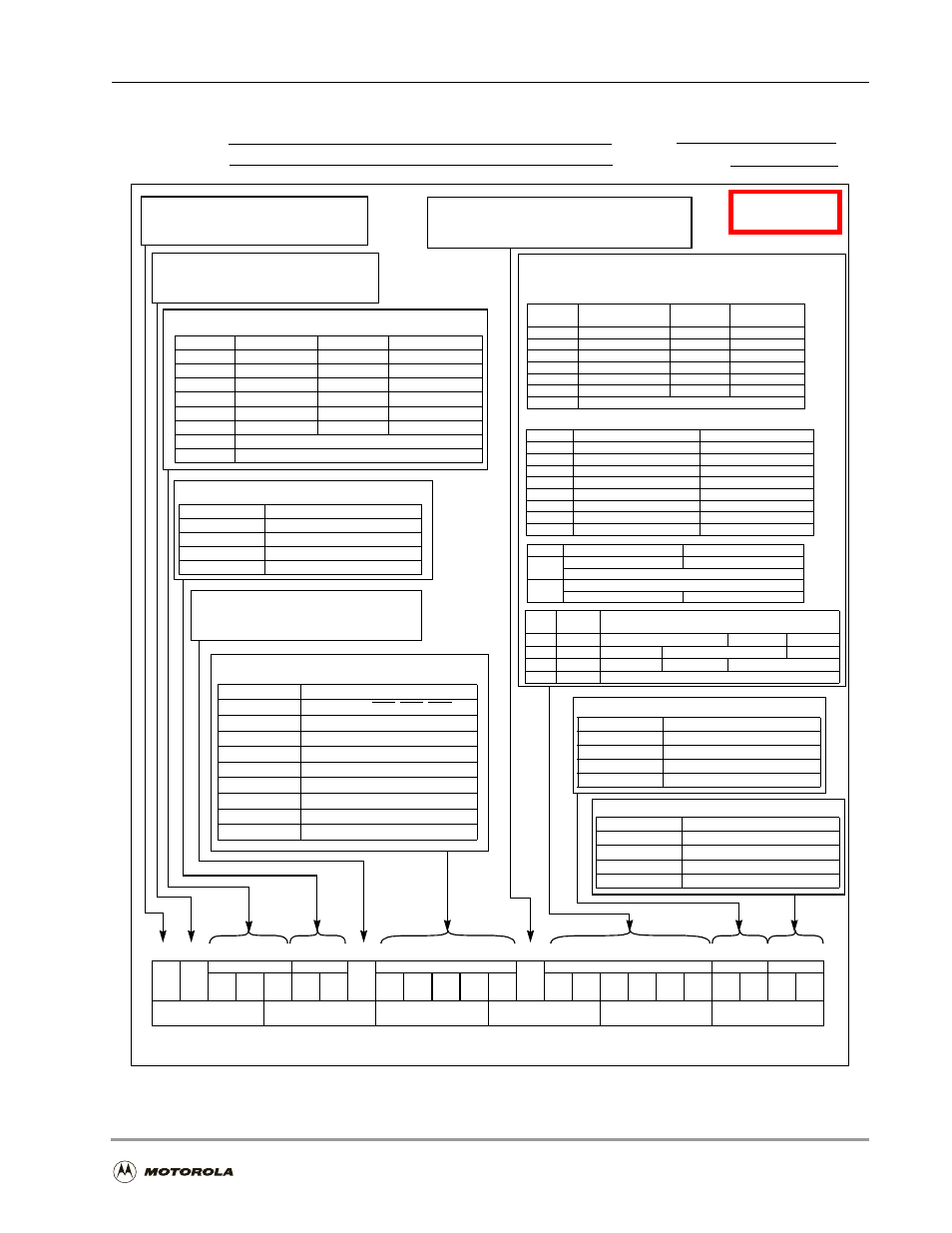

Figure B-9. DMA Control Registers 5–0 (DCR[5–0])

DMA Control Registers (DCR5–DCR0)

Reset = $000000

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

19 18 17 16

23 22 21 20

DMA Channel Enable, Bit 23

0 = Disables channel operation

1 = Enables channel operation

DMA Interrupt Enable, Bit 22

0 = Disables DMA Interrupt

1 = Enables DMA interrupt

DMA Continuous Mode Enable, Bit 16

0 = Disables continuous mode

1 = Enables continuous mode

Three-Dimensional Mode, Bit 10

0 = Three-Dimensional mode disabled

DMA Transfer Mode, Bits 21–19

DTM[2:0]

Triggered By

DE Cleared

Transfer Mode

000

request

yes

block transfer

001

request

yes

word transfer

010

request

yes

line transfer

011

DE

yes

block transfer

100

request

no

block transfer

101

request

no

word transfer

110

reserved

111

reserved

1 = Three-Dimensional mode enabled

DMA Channel Priority, Bits 18–17

DPR[1:0]

Channel Priority

00

Priority level 0 (lowest)

01

Priority level 1

10

Priority level 2

11

Priority level 3 (highest)

DMA Source Space, Bits 1–0

DSS[1:0]

DMA Source Memory

00

X Memory Space

01

Y Memory Space

10

P Memory Space

11

Reserved

DMA Destination Space, Bits 3–2

DSS[1:0]

DMA Destination Memory

00

X Memory Space

01

Y Memory Space

10

P Memory Space

11

Reserved

DMA Request Source, Bits 15–11

DRS[4:0]

Requesting Device

00000–00011

External (IRQA, IRQB, IRQC, IRQD)

00100–01001

Transfer done from channel 0,1,2,3,4,5

01010–01011

ESSI0 Receive, Transmit Data

01100–01101

ESSI1 Receive, Transmit Data

01110–01111

SCI Receive, Transmit Data

10000–10010

Timer0, Timer1, Timer2

10011

Host Receive Data Full

10100

Host Transmit Data Empty

10101 - 11111

Reserved

DMA Address Mode, Bits 9–4

Non-Three-Dimensional Addressing Modes (D3D=0)

Three-Dimensional Addressing Modes (D3D=1)

DAM[5–3]

DAM[2–0]

Addressing Mode

Counter

Mode

Offset Register

Selection

000

2D

B

DOR0

001

2D

B

DOR1

010

2D

B

DOR2

011

2D

B

DOR3

100

No update

A

None

101

Postincrement-by-1

A

None

110–111

reserved

DAM[5–3]

Addressing Mode

Offset Selection

000

2D

DOR0

001

2D

DOR1

010

2D

DOR2

011

2D

DOR3

100

No update

None

101

Postincrement-by-1

None

110

3D

DOR[0–1]

111

3D

DOR[2–3]

DAM[2–0] = source

DAM[5–3] = Destination

DMA

Application:

Date:

Programmer:

Sheet 1 of 1

DRS[4–0]

DE

DTM[2–0]

DAM[5–0]

DDS[1–0]

DSS[1–0]

DIE

DPR[1–0] DCON

D3D

X:$FFFFE4, X:$FFFFE8, X:$FFFFEC

Read/Write

X:$FFFFD8, X:$FFFFDC, X:$FFFFE0,

DAM2

Addressing Mode

Offset Selection

0

Source: 3D

Source: DOR[0–1]

Destination: Defined by DAM[5–3]

1

Source: Defined by DAM[5–3]

Destination: 3D

Destination: DOR[2–3]

DAM

[1–0]

Counter

DCO Layout

00

Mode C

DCOH[23–12]

DCOM[11–6] DCOL[5–0]

01

Mode D DCOH[23–18]

DCOM[17–6]

DCOL[5–0]

10

Mode E DCOH[23–18] DCOM[17–12]

DCOL[11–0]

11

—

Reserved