Motorola DSP56301 User Manual

Page 254

SCI Programming Model

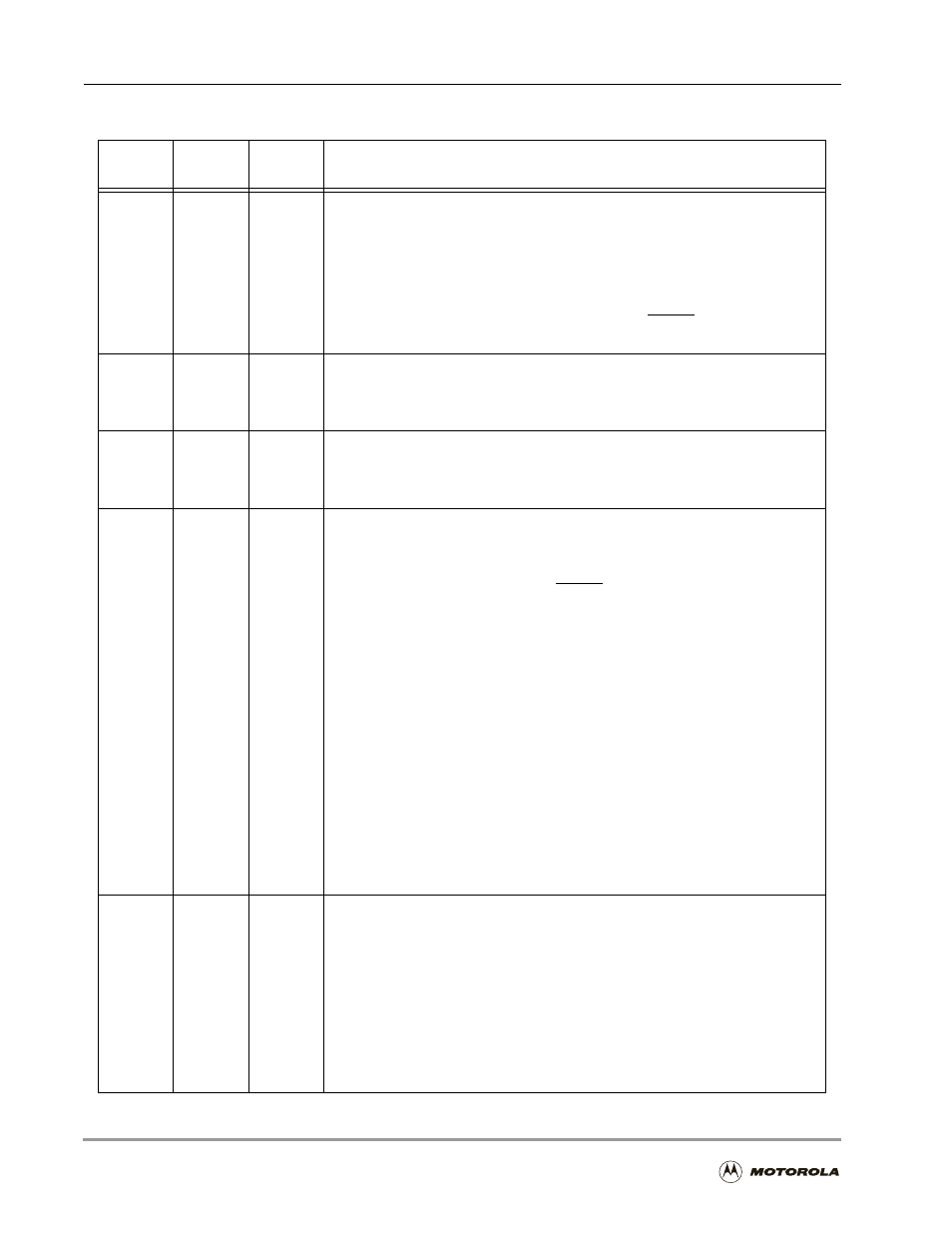

8

-18

DSP56301 User’s Manual

4

OR

0

Overrun Error Flag

Set when a byte is ready to be transferred from the receive shift register to the

receive data register (SRX) that is already full (RDRF = 1). The receive shift

register data is not transferred to the SRX. The OR flag indicates that

character(s) in the received data stream may have been lost. The only valid data

is located in the SRX. OR is cleared when the SCI status register is read,

followed by a read of SRX. The OR bit clears the FE and PE bits; that is, overrun

error has higher priority than FE or PE. A hardware RESET signal, a software

RESET instruction, an SCI individual reset, or a STOP instruction clears OR.

3

IDLE

0

Idle Line Flag

Set when 10 (or 11) consecutive ones are received. IDLE is cleared by a start-bit

detection. The IDLE status bit represents the status of the receive line. The

transition of IDLE from 0 to 1 can cause an IDLE interrupt (ILIE).

2

RDRF

0

Receive Data Register Full

Set when a valid character is transferred to the SCI receive data register from

the SCI receive shift register (regardless of the error bits condition). RDRF is

cleared when the SCI receive data register is read.

1

TDRE

1

Transmit Data Register Empty

Set when the SCI transmit data register is empty. When TDRE is set, new data

can be written to one of the SCI transmit data registers (STX) or the transmit

data address register (STXA). TDRE is cleared when the SCI transmit data

register is written. Either a hardware RESET signal, a software RESET

instruction, an SCI individual reset, or a STOP instruction sets TDRE.

In Synchronous mode, when the internal SCI clock is in use, there is a delay of

up to 5.5 serial clock cycles between the time that STX is written until TDRE is

set, indicating the data has been transferred from the STX to the transmit shift

register. There is a delay of 2 to 4 serial clock cycles between writing STX and

loading the transmit shift register; in addition, TDRE is set in the middle of

transmitting the second bit. When using an external serial transmit clock, if the

clock stops, the SCI transmitter stops. TDRE is not set until the middle of the

second bit transmitted after the external clock starts. Gating the external clock off

after the first bit has been transmitted delays TDRE indefinitely.

In Asynchronous mode, the TDRE flag is not set immediately after a word is

transferred from the STX or STXA to the transmit shift register nor when the

word first begins to be shifted out. TDRE is set 2 cycles (of the 16

×

clock) after

the start bit; that is, 2 (16

×

clock) cycles into the transmission time of the first

data bit.

0

TRNE

1

Transmitter Empty

This flag bit is set when both the transmit shift register and transmit data register

(STX) are empty, indicating that there is no data in the transmitter. When TRNE

is set, data written to one of the three STX locations or to the transmit data

address register (STXA) is transferred to the transmit shift register and is the first

data transmitted. TRNE is cleared when a write into STX or STXA clears TDRE

or when an idle, preamble, or break is transmitted. When set, TRNE indicates

that the transmitter is empty; therefore, the data written to STX or STXA is

transmitted next. That is, there is no word in the transmit shift register being

transmitted. This procedure is useful when initiating the transfer of a message

(that is, a string of characters).

Table 8-4. SCI Status Register (SSR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description