Motorola DSP56301 User Manual

Page 316

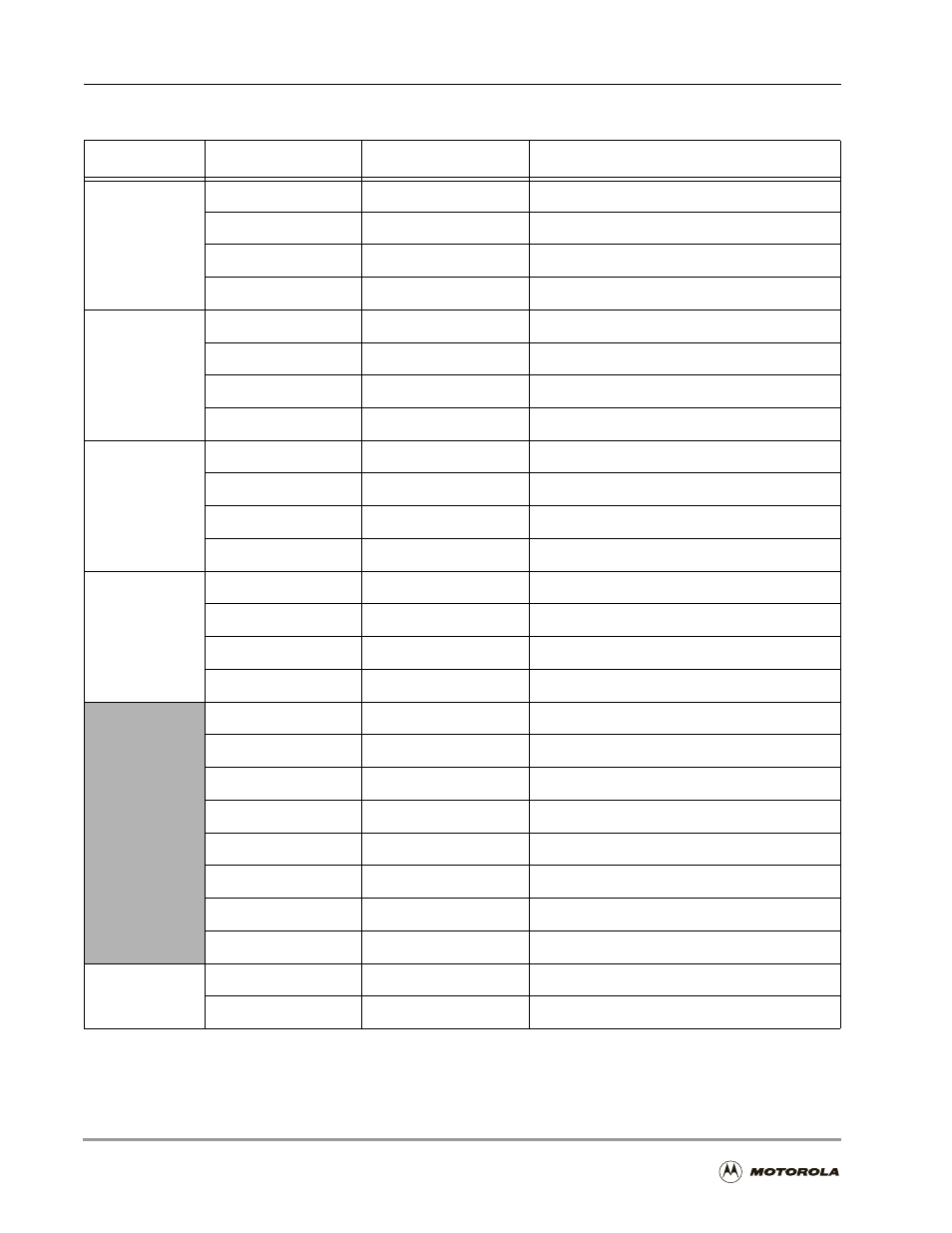

Internal I/O Memory Map

B

-4

DSP56301 User’s Manual

DMA2

$FFE7

$FFFFE7

DMA Source Address Register (DSR2)

$FFE6

$FFFFE6

DMA Destination Address Register (DDR2)

$FFE5

$FFFFE5

DMA Counter (DCO2)

$FFE4

$FFFFE4

DMA Control Register (DCR2)

DMA3

$FFE3

$FFFFE3

DMA Source Address Register (DSR3)

$FFE2

$FFFFE2

DMA Destination Address Register (DDR3)

$FFE1

$FFFFE1

DMA Counter (DCO3)

$FFE0

$FFFFE0

DMA Control Register (DCR3)

DMA4

$FFDF

$FFFFDF

DMA Source Address Register (DSR4)

$FFDE

$FFFFDE

DMA Destination Address Register (DDR4)

$FFDD

$FFFFDD

DMA Counter (DCO4)

$FFDC

$FFFFDC

DMA Control Register (DCR4)

DMA5

$FFDB

$FFFFDB

DMA Source Address Register (DSR5)

$FFDA

$FFFFDA

DMA Destination Address Register (DDR5)

$FFD9

$FFFFD9

DMA Counter (DCO5)

$FFD8

$FFFFD8

DMA Control Register (DCR5)

$FFD7

$FFFFD7

Reserved

$FFD6

$FFFFD6

Reserved

$FFD5

$FFFFD5

Reserved

$FFD4

$FFFFD4

Reserved

$FFD3

$FFFFD3

Reserved

$FFD2

$FFFFD2

Reserved

$FFD1

$FFFFD1

Reserved

$FFD0

$FFFFD0

Reserved

PORT B

$FFCF

$FFFFCF

Host Port GPIO Data Register (DATH)

$FFCE

$FFFFCE

Host Port GPIO Direction Register (DIRH)

Table B-2. Internal I/O Memory Map (X Data Memory) (Continued)

Peripheral

16-Bit Address

24-Bit Address

Register Name