Hi32 (pci master data transfer formats -8, Table 6-3. hi32 (pci master data transfer formats – Motorola DSP56301 User Manual

Page 126

Data Transfer Paths

6

-8

DSP56301 User’s Manual

HRXS. Each time the host reads a 32-bit word from the HRXS, the 32-bits of significant data

located in two locations of the slave DSP-to-host data path (DTXS and HRXS) are output.

The DSP side of the DSP-to-host data FIFOs is described in the following pages. For a

detailed description of the host side, see Section 6.8.4, Host Master Receive Data Register

(HRXM), on page 6-61 and Section 6.8.5, Host Slave Receive Data Register (HRXS), on page

6-61.

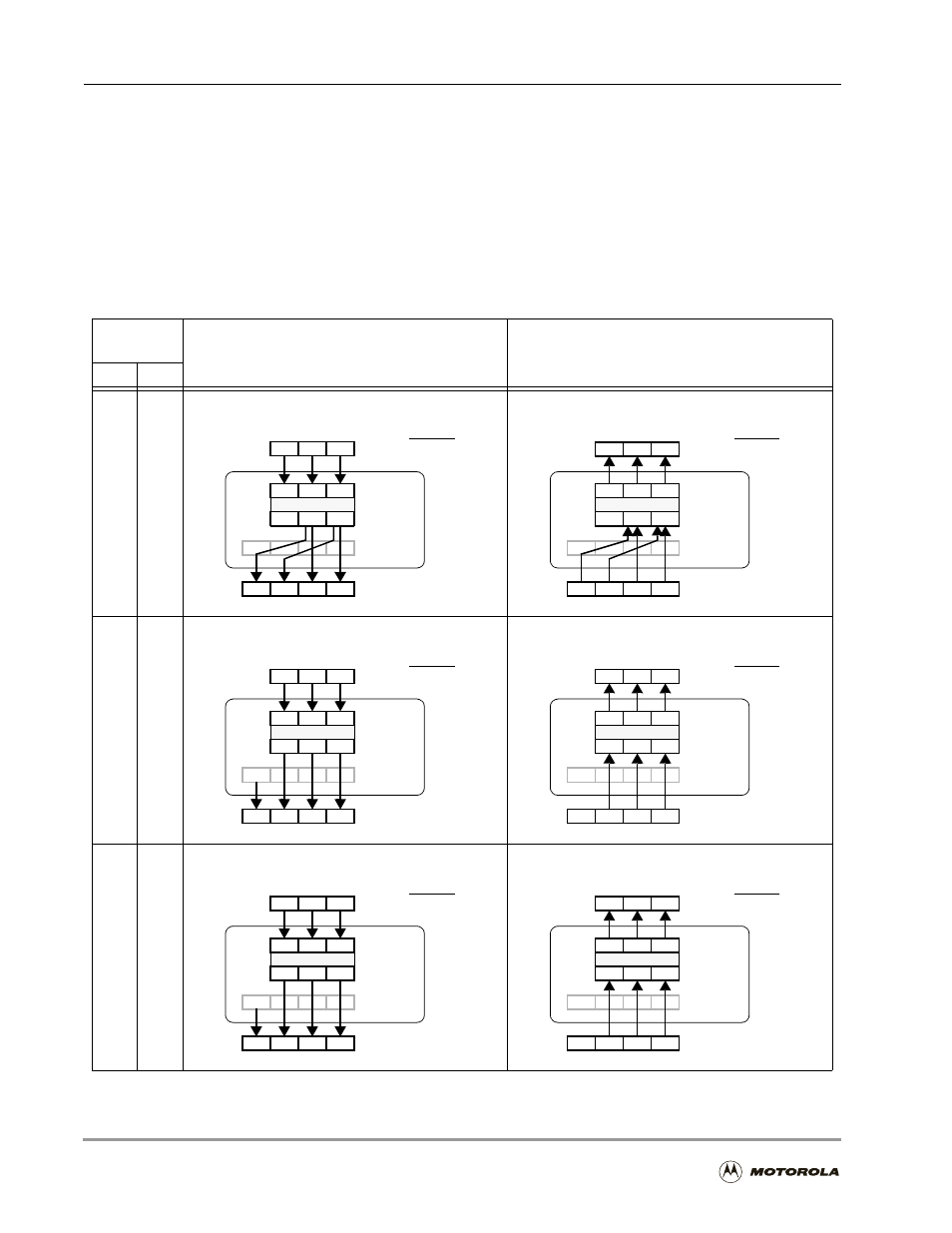

Table 6-3. HI32 (PCI Master Data Transfer Formats

DPMC

Register

DSP-to-PCI Host

Data Transfer Format

PCI Host-to-DSP

Data Transfer Format

FC1

FC0

0

0

The two least significant bytes of two HRXM

locations are output.

All 32 PCI data bits are written to the HTXR as two

zero extended 16-bit words.

0

1

The three least significant HRXM bytes are output

right aligned and zero extended.

The three least significant PCI data bytes are

written to the HTXR.

1

0

The three least significant HRXM bytes are output

right aligned and sign extended.

The three least significant PCI data bytes are

written to the HTXR.

HDTFC

PCI bus

DTXM

HI32

GDB/MDDB

HRXM

X

X

X

$0

HDTFC

PCI bus

DRXR

HI32

GDB/MDDB

HTXR

$0

HDTFC

PCI bus

DTXM

HI32

GDB/MDDB

$0

$0

HRXM

HDTFC

PCI bus

DRXR

HI32

GDB/MDDB

X

HTXR

HDTFC

PCI bus

DTXM

HI32

GDB/MDDB

S

S

HRXM

HDTFC

PCI bus

DRXR

HI32

GDB/MDDB

X

HTXR