2 operation, 1 timer after reset, Operation -3 – Motorola DSP56301 User Manual

Page 265: Timer after reset -3, Timer module block diagram -3, 2 operation, 1 timer after reset, Reset, Initialization, Exceptions

Operation

Triple Timer Module

9

-3

The timer mode is controlled by the TC[3–0] bits which are TCSR[7–4]. For a listing of the

timer modes and descriptions of their operations, see Section 9.3, Operating Modes, on page

9-5.

.

9.2

Operation

This section discusses the following timer basics:

n

Reset

n

Initialization

n

Exceptions

9.2.1

Timer After Reset

A hardware

RESET

signal or software RESET instruction clears the Timer Control and Status

Register for each timer, thus configuring each timer as a GPIO. A timer is active only if the

timer enable bit 0 (TCSR[TE]) in the specific timer TCSR is set.

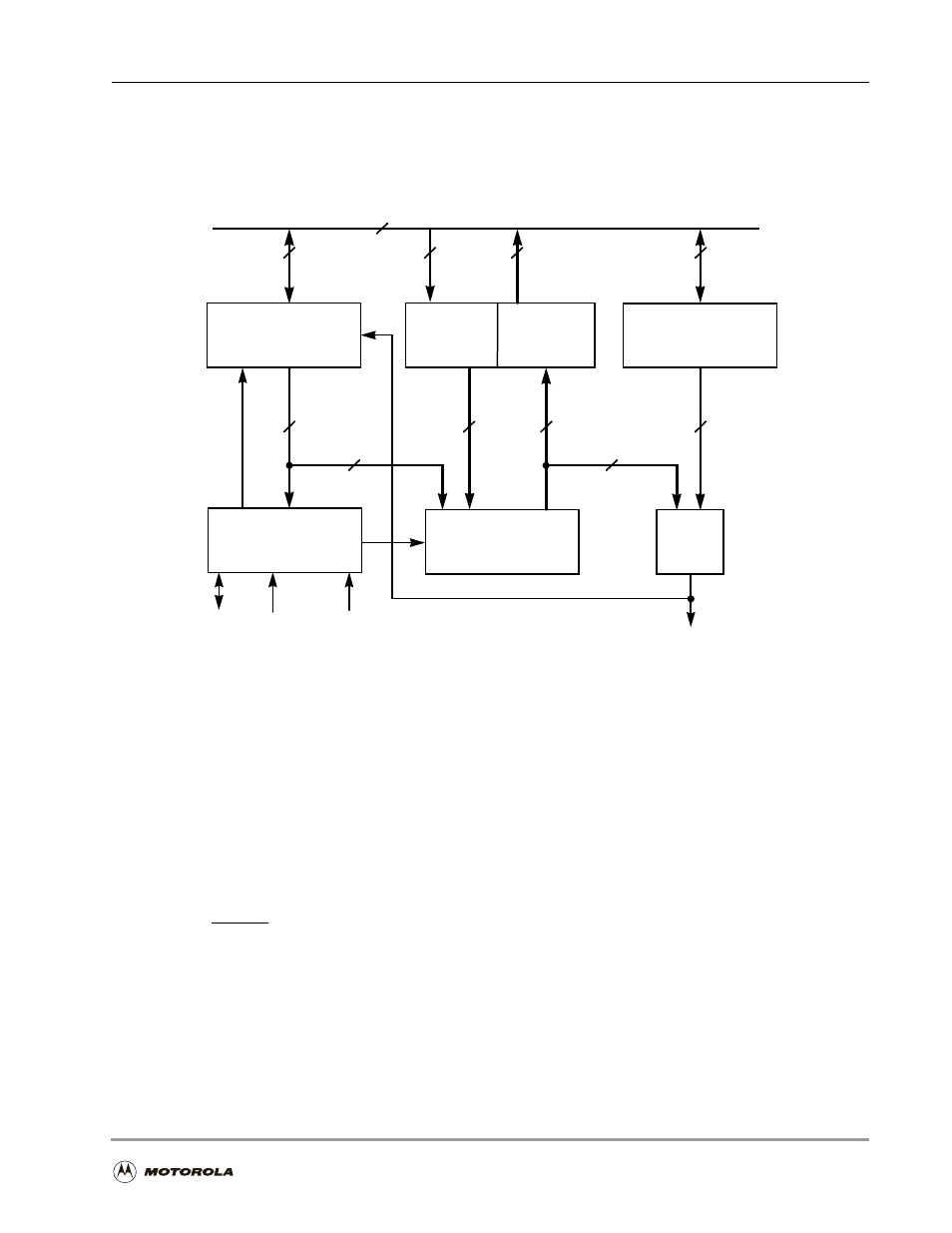

Figure 9-2. Timer Module Block Diagram

GDB

Control/Status

Register

TCSR

Counter

Timer interrupt/DMA request

Timer Control

CLK/2

TIO

Compare

Register

TCPR

=

24

24

Logic

Load

Register

Count

Register

TLR

Prescaler CLK

TCR

24

24

9

2

24

24

24

24

24