Motorola DSP56301 User Manual

Page 48

Host Interface (HI32)

2

-18

DSP56301 User’s Manual

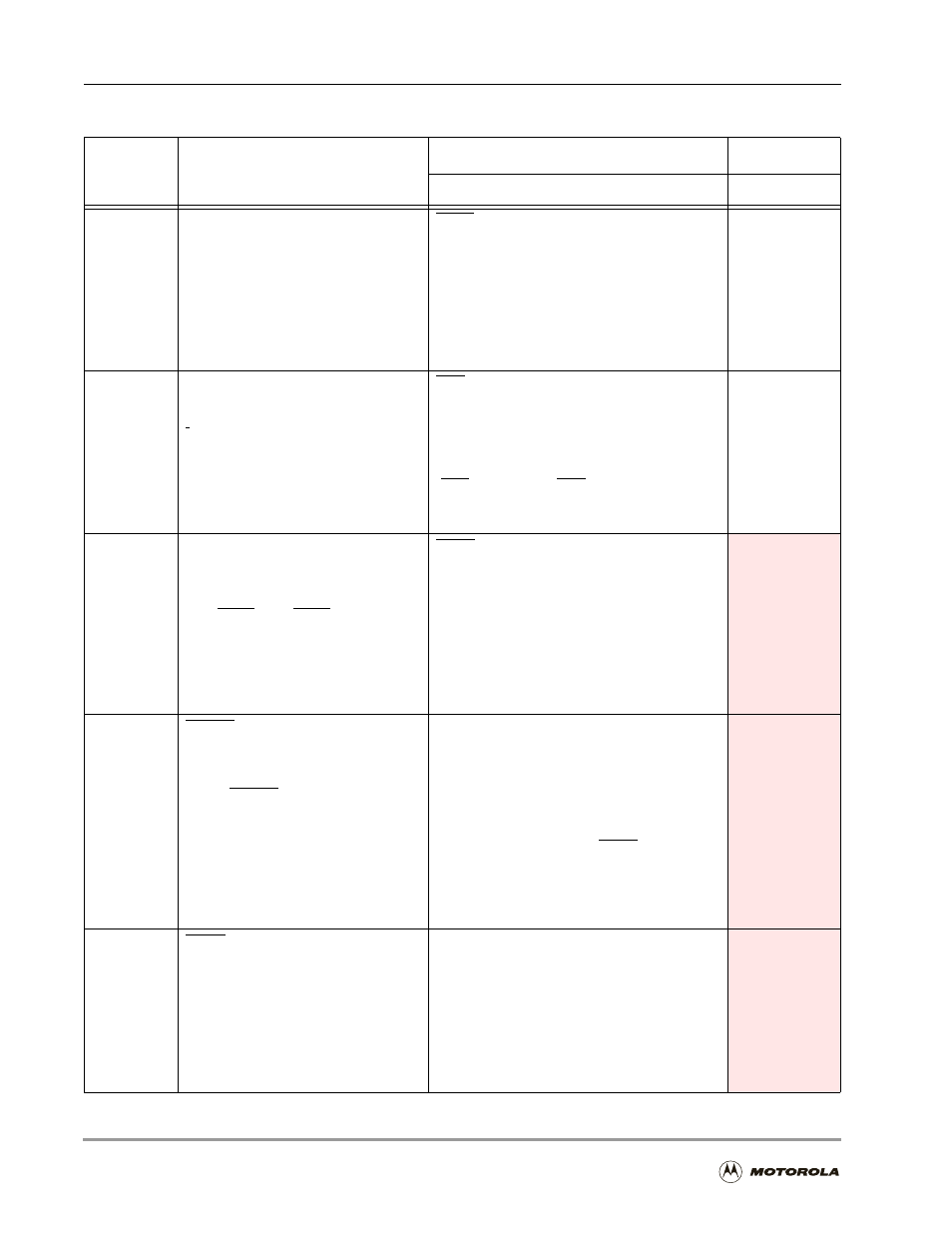

HP22

HDEVSEL

Host Device Select

Sustained tri-state bidirectional pin.

2

When actively driven, indicates the

driving device has decoded its

address as a target of the current

access. As an input it indicates

whether any device on the bus is

selected.

HSAK

Host Select Acknowledge

Active low output pin.

Acknowledges to the host processor that the

HI32 has identified its address as a slave.

HSAK is asserted when the HI32 is the

selected slave; otherwise HSAK is released.

HI022

GPIO

2

HP23

HLOCK

Host Lock

Sustained tri-state bidirectional pin.

2

Indicates an atomic operation that

may require multiple transactions to

complete. When HLOCK is asserted,

non-exclusive transactions to the

HI32 are ‘retried’ (that is, this is an

entire resource lock).

HBS

Bus Strobe

Schmitt trigger input pin.

Asserted at the start of a bus cycle (for half of

a clock cycle) providing an “early bus start”

signal. This enables the HI32 to respond

(HTA valid) earlier. HBS should be forced or

pulled up to V

CC

if not used (for example, ISA

bus).

HIO23

GPIO

2

HP24

HPAR

Host Parity

Tri-state bidirectional pin.

Even parity across HAD[31–0] and

HC3/HBE3–HC0/HBE0. The master

drives HPAR during address and write

data phases; the target drives HPAR

during read data phases.

HDAK

Host DMA Acknowledge

Schmitt trigger input pin.

Indicates that the external DMA channel is

accessing the HI32. The HI32 is selected as a

DMA device if HDAK and HWR or HRD (in the

double-strobe mode) or HDAK and HDS (in

the single-strobe mode) are asserted. HDAK

should be forced or pulled up to V

CC

if not

used.

disconnected

HP25

HPERR

Parity Error

Sustained tri-state bidirectional pin.

2

Used for reporting of data parity

errors. HPERR must be driven active

(by the agent receiving data) two

clocks following the data (that is one

clock following the HPAR signal)

when a data parity error is detected.

HDRQ

DMA Request

Output Pin.

Supports ISA/EISA-type DMA data transfers.

The HI32 asserts HDRQ when a DMA request

(receive and/or transmit) is generated in the

HI32. HDRQ is deasserted when the DMA

request source is cleared (HDAK is asserted),

masked (by RREQ=0 or TREQ=0) or disabled

(DMAE=0).

The polarity of HDRQ pin is controlled by

HDRP bit in the DCTR.

disconnected

HP26

HGNT

Bus Grant

Input pin.

Indicates to the HI32 that it has

mastership of the bus. If not used, this

pin should be forced or pulled up to

Vcc.

HAEN

Host Address Enable

Input pin.

Enables ISA/EISA DMA / I/O type accesses.

When high, the HI32 responds to DMA cycles

only (if DMAE=1 in the DCTR; if DMAE=0, the

HI32 ignores the access). When low, the HI32

responds when it identifies its address (that is

ISA/EISA DMA / I/O type-space accesses).

disconnected

Table 2-12. Host Port Pins (HI32) (Continued)

Signal

Name

PCI

Universal Bus Mode

Enhanced Universal Bus Mode

GPIO