Motorola DSP56301 User Manual

Page 83

Central Processor Unit (CPU) Registers

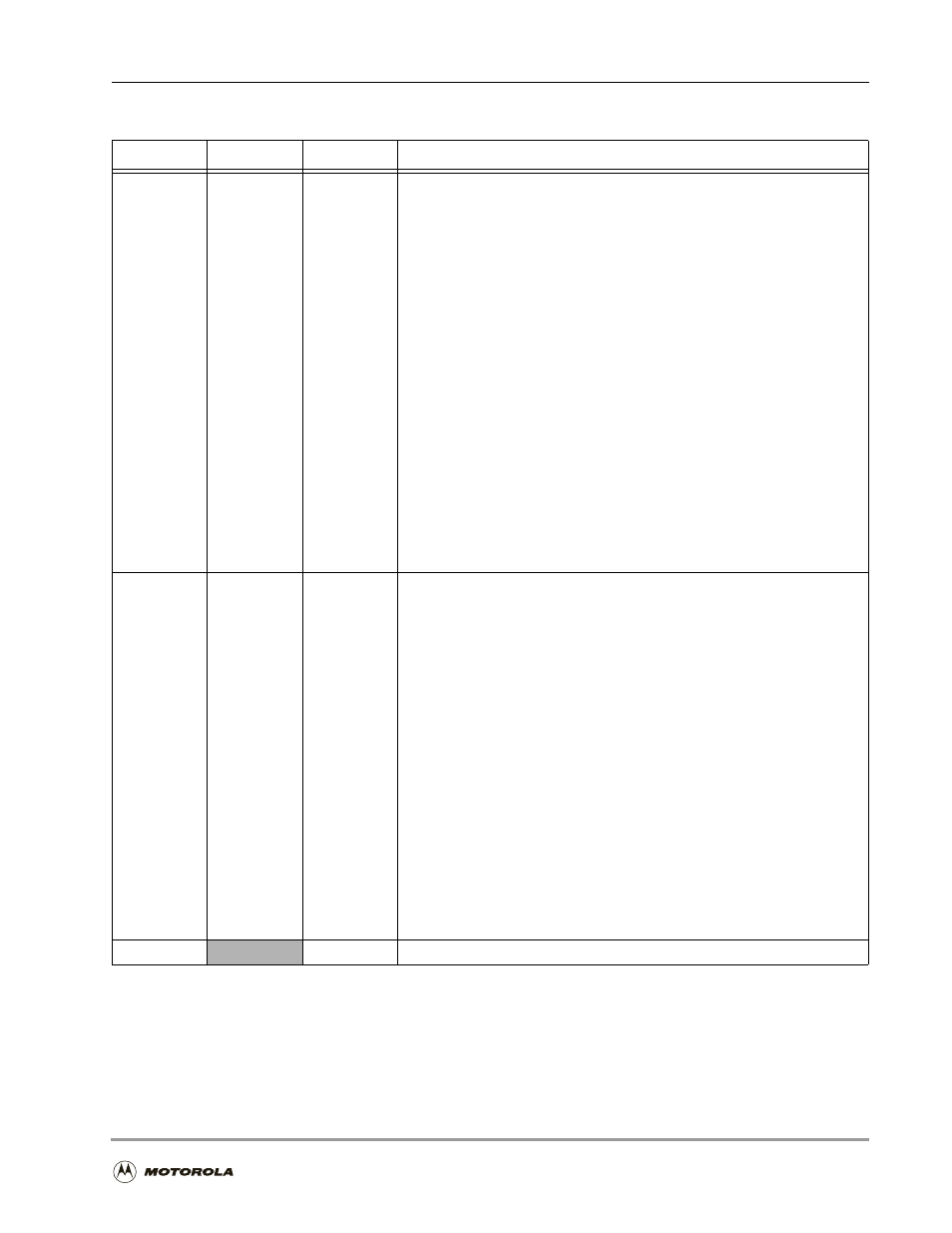

Core Configuration

4

-9

14

DM

0

Double-Precision Multiply Mode

Enables four multiply/MAC operations to implement a double-precision

algorithm that multiplies two 48-bit operands with a 96-bit result. Clearing

the DM bit disables the mode.

Note:

The Double-Precision Multiply mode is supported to maintain

object code compatibility with devices in the DSP56000 family. For

a more efficient way of executing double precision multiply, refer

to the chapter on the Data Arithmetic Logic Unit in the

DSP56300

Family Manual.

In Double-Precision Multiply mode, the behavior of the four specific

operations listed in the double-precision algorithm is modified. Therefore,

do not use these operations (with those specific register combinations) in

Double-Precision Multiply mode for any purpose other than the double

precision multiply algorithm. All other Data ALU operations (or the four

listed operations, but with other register combinations) can be used.

The double-precision multiply algorithm uses the Y0 Register at all stages.

Therefore, do not change Y0 when running the double-precision multiply

algorithm. If the Data ALU must be used in an interrupt service routine, Y0

should be saved with other Data ALU registers to be used and restored

before the interrupt routine terminates.

13

SC

0

Sixteen-Bit Compatibility Mode

Affects addressing functionality, enabling full compatibility with object code

written for the DSP56000 family. When SC is set, MOVE operations to/from

any of the following PCU registers clear the eight MSBs of the destination:

LA, LC, SP, SSL, SSH, EP, SZ, VBA and SC. If the source is either the SR

or OMR, then the eight MSBs of the destination are also cleared. If the

destination is either the SR or OMR, then the eight MSBs of the destination

are left unchanged. To change the value of one of the eight MSBs of the SR

or OMR, clear SC.

SC also affects the contents of the Loop Counter Register. If SC is cleared

(normal operation), then a loop count value of zero causes the loop body to

be skipped, and a loop count value of $FFFFFF causes the loop to execute

the maximum number of 2

24

– 1 times. If the SC bit is set, a loop count

value of zero causes the loop to execute 2

16

times, and a loop count value

of $FFFFFF causes the loop to execute 2

16

– 1 times.

Note:

Due to pipelining, a change in the SC bit takes effect only after

three instruction cycles. Insert three NOP instructions after the

instruction that changes the value of this bit to ensure proper

operation.

12

0

Reserved. Write to 0 for future compatibility.

Table 4-3. Status Register Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description