2 operating mode register (omr), Operating mode register (omr) -12, Operating mode register (omr) bit definitions -12 – Motorola DSP56301 User Manual

Page 86: 2 operating mode register (omr)

Central Processor Unit (CPU) Registers

4

-12

DSP56301 User’s Manual

4.3.2

Operating Mode Register (OMR)

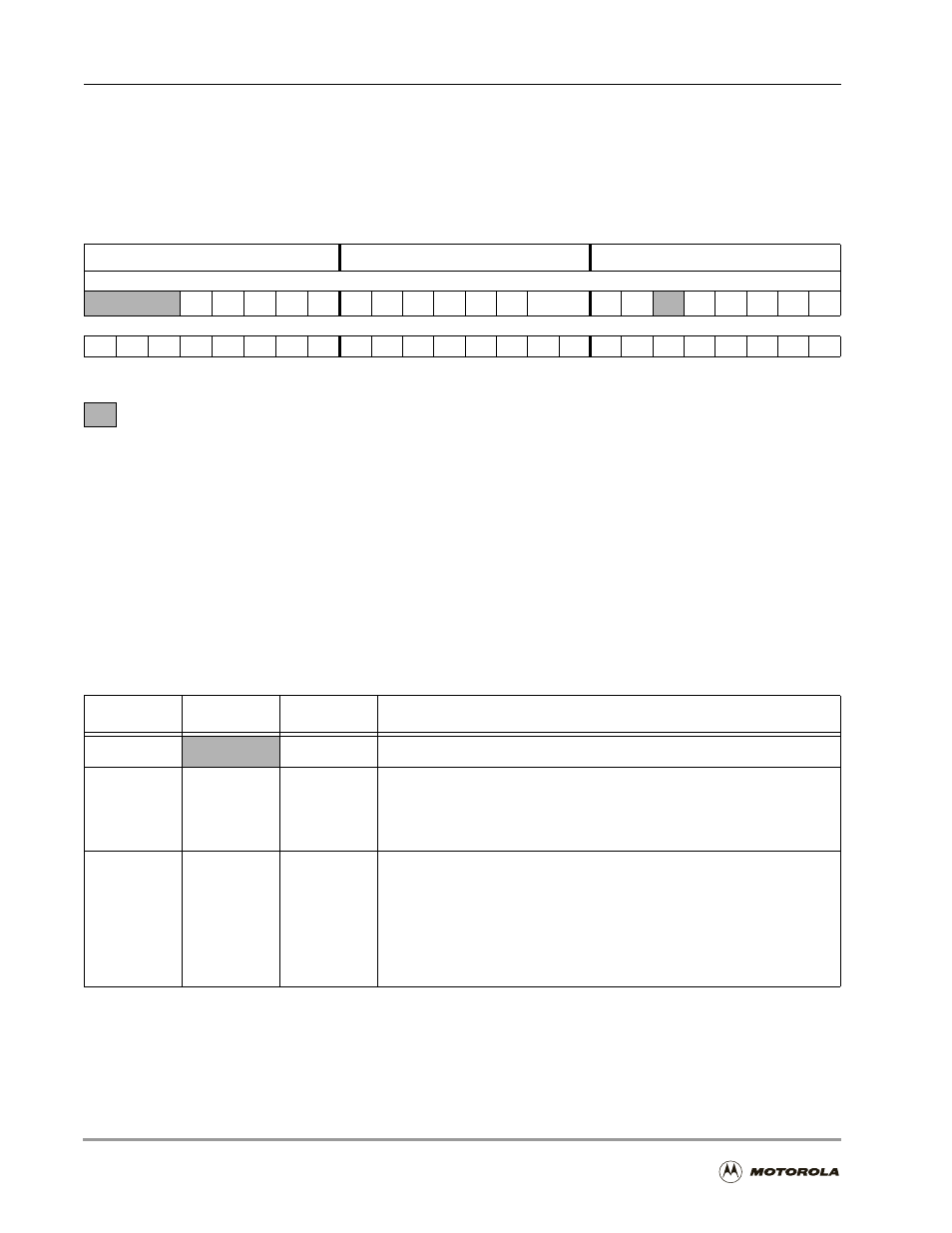

The OMR is a read/write register divided into three byte-sized units. The lowest two bytes

(EOM and COM) control the chip’s operating mode. The high byte (SCS) controls and

monitors the stack extension. The OMR control bits are shown in Figure 4-2.

The Enhanced Operating Mode (EOM) and Chip Operating Mode (COM) bytes are affected

only by processor reset and by instructions directly referencing the OMR (that is, ANDI, ORI,

and other instructions, such as MOVEC, that specify OMR as a destination). The Stack

Control/Status (SCS) byte is referenced implicitly by some instructions, such as DO, JSR, and

RTI, or directly by the MOVEC instruction. During processor reset, the chip operating mode

bits (MD, MC, MB, and MA) are loaded from the external mode select pins MODD–MODA,

respectively. Table 4-4 defines the DSP56301 OMR bits.

Stack Control/Status (SCS)

Extended Operating Mode (EOM)

Chip Operating Mode (COM)

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SEN WRP EOV EUN XYS ATE APD ABE BRT TAS BE

CDP[1–0] MS

SD

EBD MD

MC

MB

MA

Reset:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

*

*

*

*

*

After reset, these bits reflect the corresponding value of the mode input (that is, MODD, MODC, MODB, or MODA,

respectively).

Reserved bit. Read as zero; write to zero for future compatibility

Figure 4-2. Operating Mode Register (OMR)

Table 4-4. Operating Mode Register (OMR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–21

0

Reserved. Write to 0 for future compatibility.

20

SEN

0

Stack Extension Enable

Enables/disables the stack extension in data memory. If the SEN bit is set,

the extension is enabled. Hardware reset clears this bit, so the default out

of reset is a disabled stack extension.

19

WRP

0

Stack Extension Wrap Flag

Set when copying from the on-chip hardware stack (System Stack

Register file) to the stack extension memory begins. You can use this flag

during the debugging phase of the software development to evaluate and

increase the speed of software-implemented algorithms. The WRP flag is

a

sticky bit (that is, cleared only by hardware reset or by an explicit

MOVEC operation to the OMR).