2 port direction registers (prrc and prrd), Port direction registers (prrc and prrd) -37, Essi port signal configurations -37 – Motorola DSP56301 User Manual

Page 235: 2 port direction registers (prrc and prrd)

GPIO Signals and Registers

Enhanced Synchronous Serial Interface (ESSI)

7

-37

7.6.2

Port Direction Registers (PRRC and PRRD)

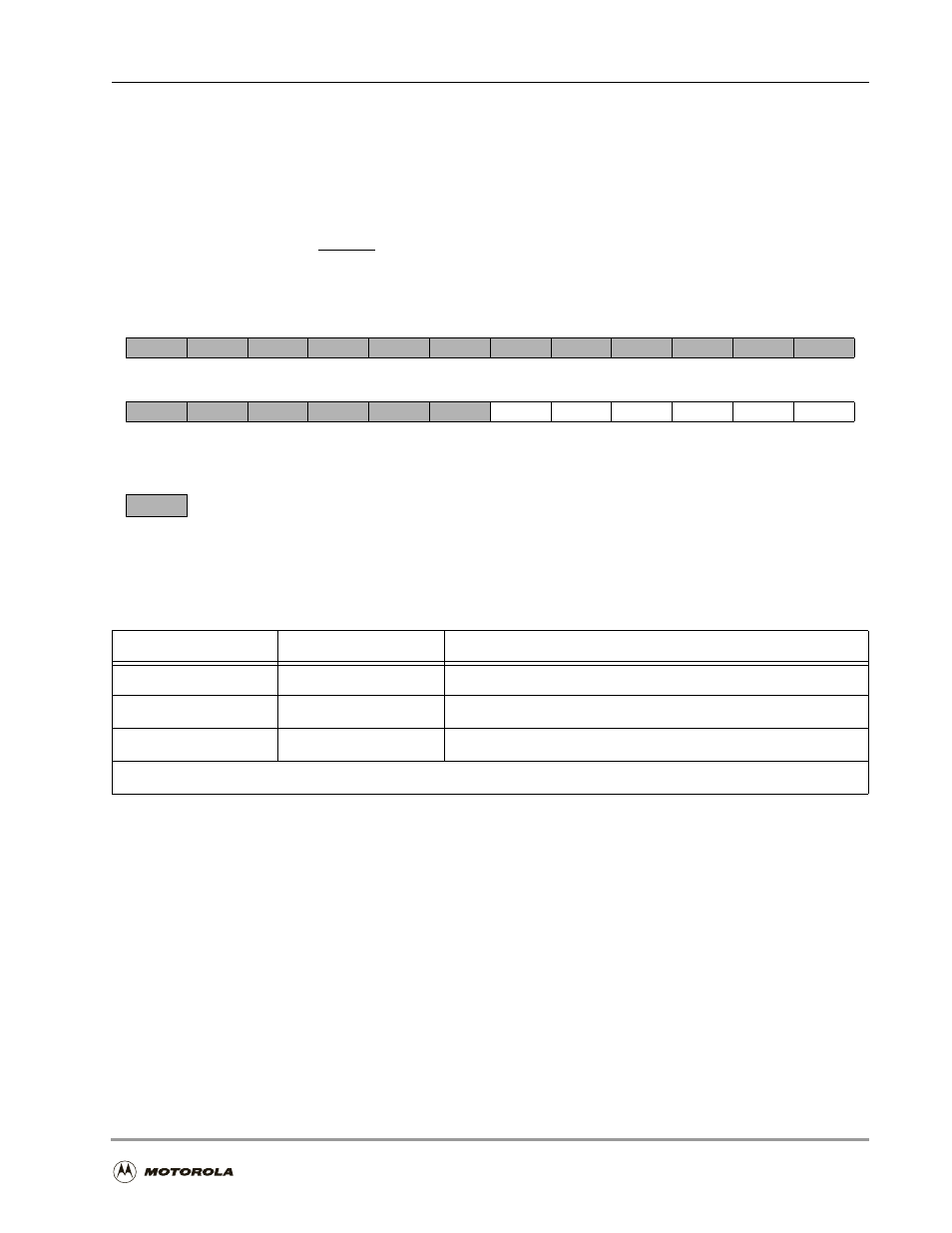

The read/write PRRC and PRRD control the data direction of the ESSI0 and ESSI1 GPIO

signals when they are enabled by the associated Port Control Register (PCRC or PCRD,

respectively). When PRRC[i] or PRRD[i] is set, the corresponding signal is an output (GPO)

signal. When PRRC[i] or PRRD[i] is cleared, the corresponding signal is an input (GPI)

signal. Either a hardware

RESET

signal or a software RESET instruction clears all PRRC and

PRRD bits.

The following table summarizes the ESSI port signal configurations.

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PRx5

PRx4

PRx3

PRx2

PRx1

PRx0

Note:

For bits 5–0, a 0 configures PRxn as a GPI and a 1 configures PRxn as a GPO. For ESSI0, the GPIO signals

are PC[5–0]. For ESSI1, the GPIO signals are PD[5–0]. The corresponding direction bits for Port C GPIOs

are PRC[5–0]. The corresponding direction bits for Port D GPIOs are PRD[5–0].

= Reserved. Read as zero. Write with zero for future compatibility.

Figure 7-19. Port Direction Registers (PRRC X:$FFFFBE) (PRRD X: $FFFFAE)

Table 7-6. ESSI Port Signal Configurations

PCRC/PCRD[i]

PRRC/PRRD[i]

Port Signal[i] Function

1

X

ESSI0/ESSI1

0

0

Port C/Port D GPI

0

1

Port C/Port D GPO

X: The signal setting is irrelevant to the Port Signal[i] function.