Error counter clear input – Yaskawa Large Capacity Sigma II Series User Manual

Page 97

4.2 Settings According to Host Controller

4-21

4

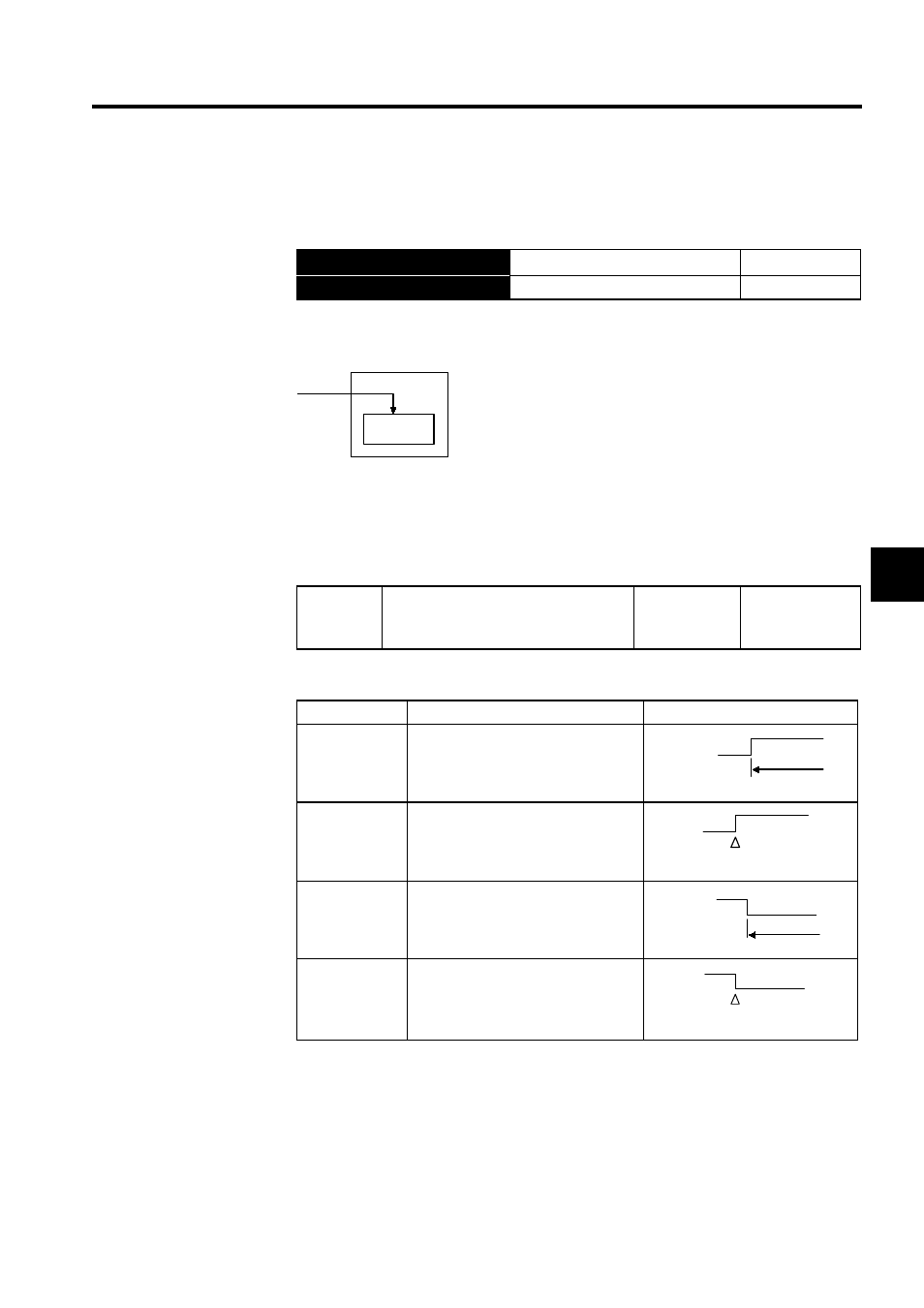

Error Counter Clear Input

The procedure for clearing the error counter is described below.

The following occurs when the CLR signal is set to high level.

• The error counter inside the SERVOPACK is set to 0.

• Position loop control is prohibited.

Use this signal to clear the error counter from the host controller or select the following clear

operation through parameter Pn200.1

Select the pulse form for the error counter clear signal CLR (CN1-15).

→ Input CLR CN1-15

Clear Input

Position Control

→ Input /CLR CN1-14

Clear Input

Position Control

Pn200.1

Error Counter Clear Signal Form

Factory

Setting:

0

Position Control

Pn200.1 Setting

Description

Clear Timing

0

Clears the error counter when the CLR

signal goes high.

Error pulses do not accumulate as long

as the signal remains high.

1

Clears the error counter on the rising

edge of the CLR signal.

Clears the error counter only once on

the rising edge of the CLR signal.

2

Clears the error counter when the CLR

signal goes low.

Error pulses do not accumulate as long

as the signal remains low.

3

Clears the error counter on the falling

edge of the CLR signal.

Clears the error counter only once on

the falling edge of the CLR signal.

SERVOPACK

CLR

Clear

Position loop

error counter

High

CLR

(CN1-15)

Cleared state

Cleared only once at this point.

CLR

(CN1-15)

High

Low

CLR

(CN1-15)

Cleared state

CLR

(CN1-15)

Low

Cleared only once at this point.