FUJITSU F2MCTM-16LX User Manual

Page 663

647

APPENDIX D List of Interrupt Vectors

Note:

For a peripheral module having two interrupt causes for one interrupt number, an EI

2

OS interrupt clear

signal clears both interrupt request flags.

When EI

2

OS ends, an EI

2

OS clear signal is sent to every interrupt flag assigned to each interrupt

number.

EI

2

OS is activated when one of two interrupts assigned to an interrupt control register (ICR) is caused

while EI

2

OS is enabled. This means that an EI

2

OS descriptor that should essentially be specific to each

interrupt cause is shared by two interrupts. Therefore, while one interrupt is enabled, the other interrupt

must be disabled.

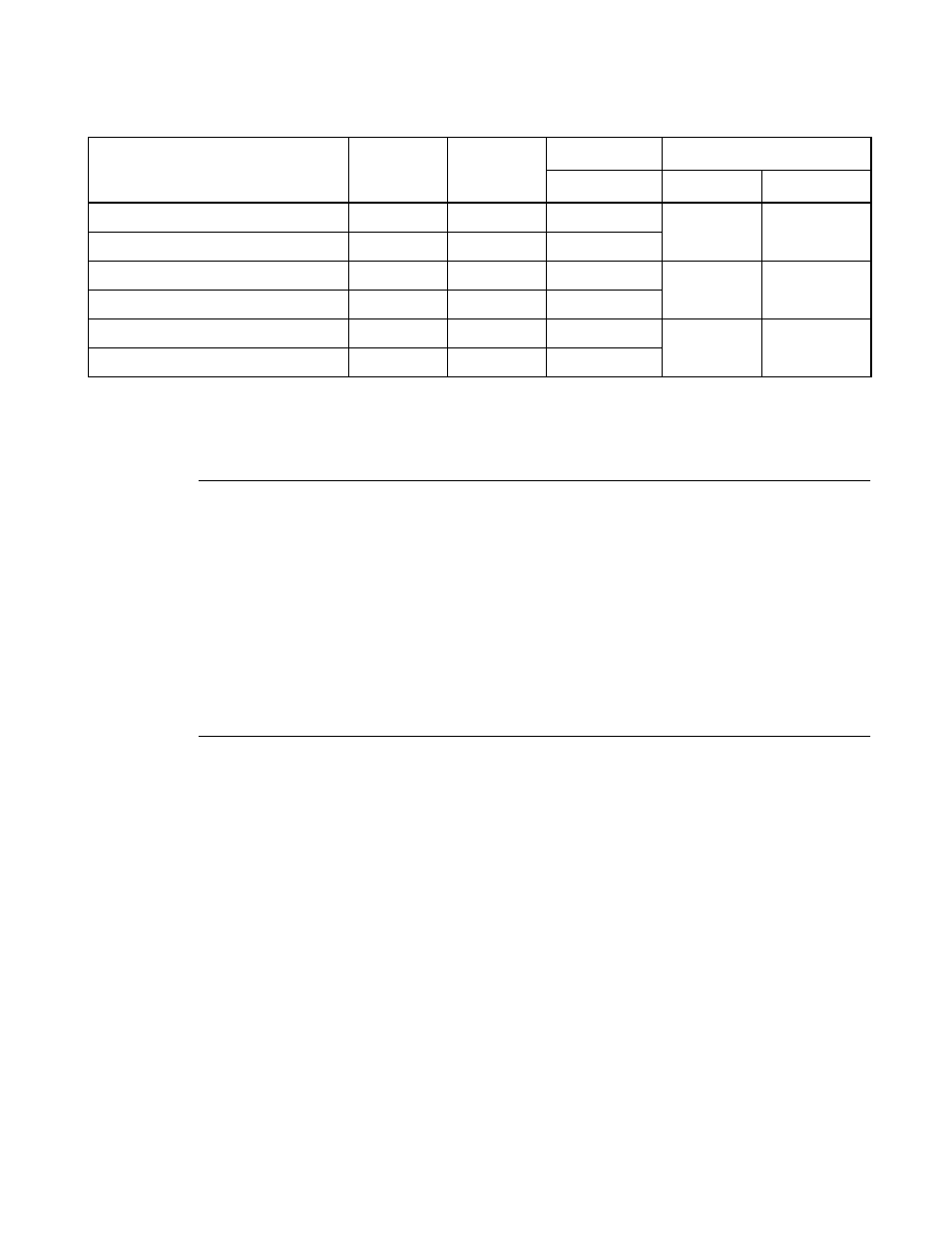

UART 1 RX

Y2

#37

FFFF68

H

ICR13

0000BD

H

UART 1 TX

Y1

#38

FFFF64

H

Reserved

N

#39

FFFF60

H

ICR14

0000BE

H

Reserved

N

#40

FFFF5C

H

Flash memory

N

#41

FFFF58

H

ICR15

0000BF

H

Delayed interrupt generation module

N

#42

FFFF54

H

Y1: An EI

2

OS interrupt clear signal or EI

2

OS register read access clears the interrupt request flag.

Y2: An EI

2

OS interrupt clear signal or EI

2

OS register read access clears the interrupt request flag. A stop request is issued.

N: An EI

2

OS interrupt clear signal does not clear the interrupt request flag.

Table D-2 Interrupt Causes, Interrupt Vectors, and Interrupt Control Registers (2/2)

Interrupt cause

EI

2

OS clear

DMA

channel

number

Interrupt vector

Interrupt control register

Number

ICR

Address