2 timer control status register (lower) (tccsl), Timer control status register (lower) (tccsl) – FUJITSU F2MCTM-16LX User Manual

Page 234

218

CHAPTER 13 16-Bit I/O TIMER

13.3.2

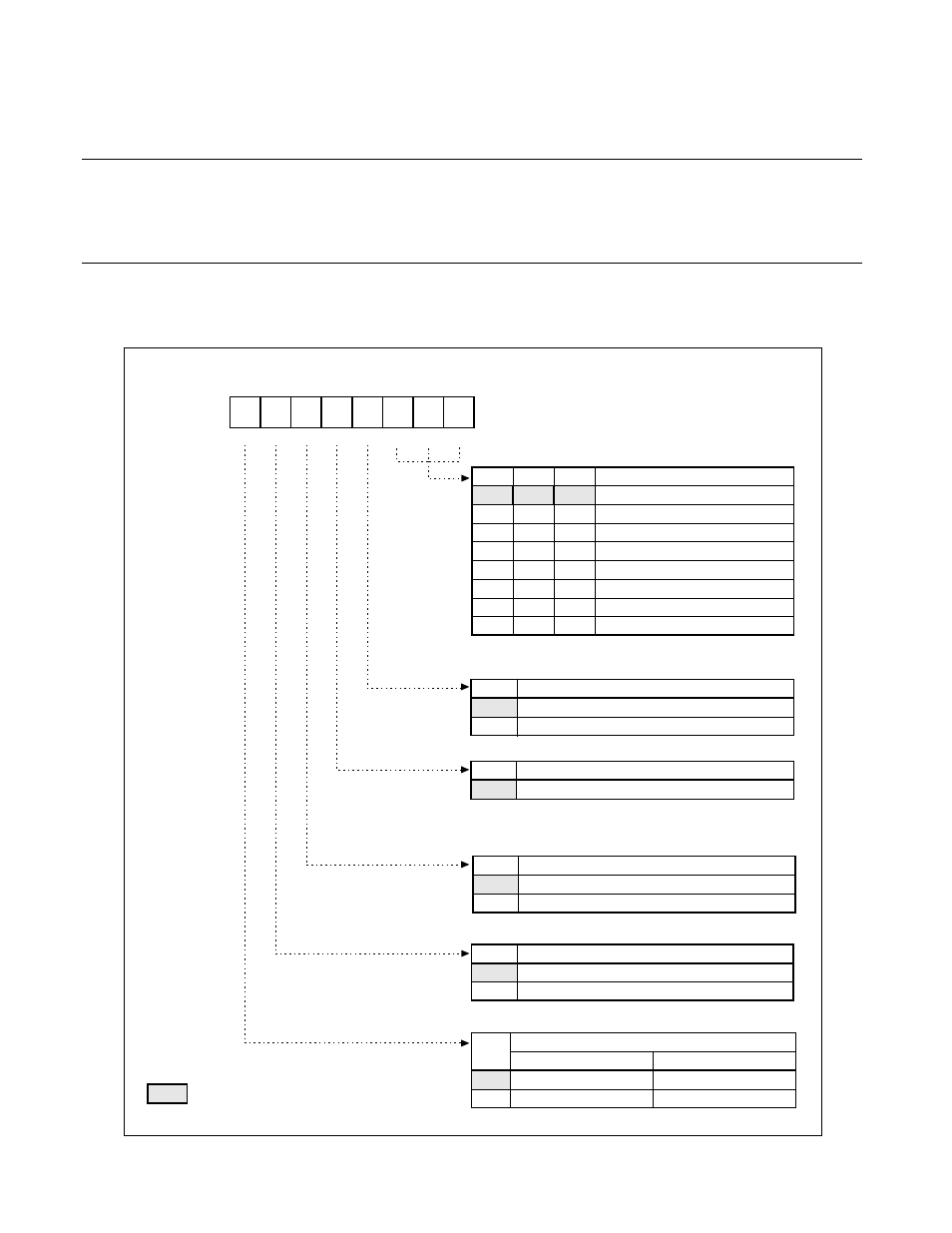

Timer Control Status Register (Lower) (TCCSL)

The timer control status register (Lower) selects the count clock and conditions for

clearing the counter, clears the counter, enables the count operation or interrupt, and

checks the interrupt request flag.

■

Timer Control Status Register (Lower) (TCCSL)

Figure 13.3-2 Timer Control Status Register (Lower) (TCCSL)

0 0 0 0 0 0 0 0

B

4

5

3

2

1

0

7

6

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

IVF IVFE STOP

Rese-

rved

CLR CLK2 CLK1 CLK0

R/W

: Read/Write

: Reset value

Reset value

φ

: Machine clock frequency

bit2

bit1

bit0

CLK2 CLK1 CLK0

Count clock cycle selection bits

0

0

0

1/

φ

0

0

1

2/

φ

0

1

0

4/

φ

0

1

1

8/

φ

1

0

0

16/

φ

1

0

1

32/

φ

1

1

0

64/

φ

1

1

1

128/

φ

bit3

CLR

Timer clear bit

0

No effect

1

Clear counter (TCDT = "0000

H

")

bit4

Reserved

Reserved bit

0

Be sure to set to "0".

bit5

STOP

Timer operation stop bit

0

Timer operating enabled

1

Timer operating disabled (stop)

bit6

IVFE

Timer overflow interrupt enable bit

0

Timer overflow interrupt disabled

1

Timer overflow interrupt enabled

bit7

IVF

Timer overflow generating flag bit

Read

Write

0

Without timer overflow

Clear this bit

1

With timer overflow

No effect

Address

TCCSL0:007942

H