5 reset cause bits, Reset cause bits – FUJITSU F2MCTM-16LX User Manual

Page 144

128

CHAPTER 7 RESETS

7.5

Reset Cause Bits

A reset cause can be identified by reading the watchdog timer control register (WDTC).

■

Reset Cause Bits

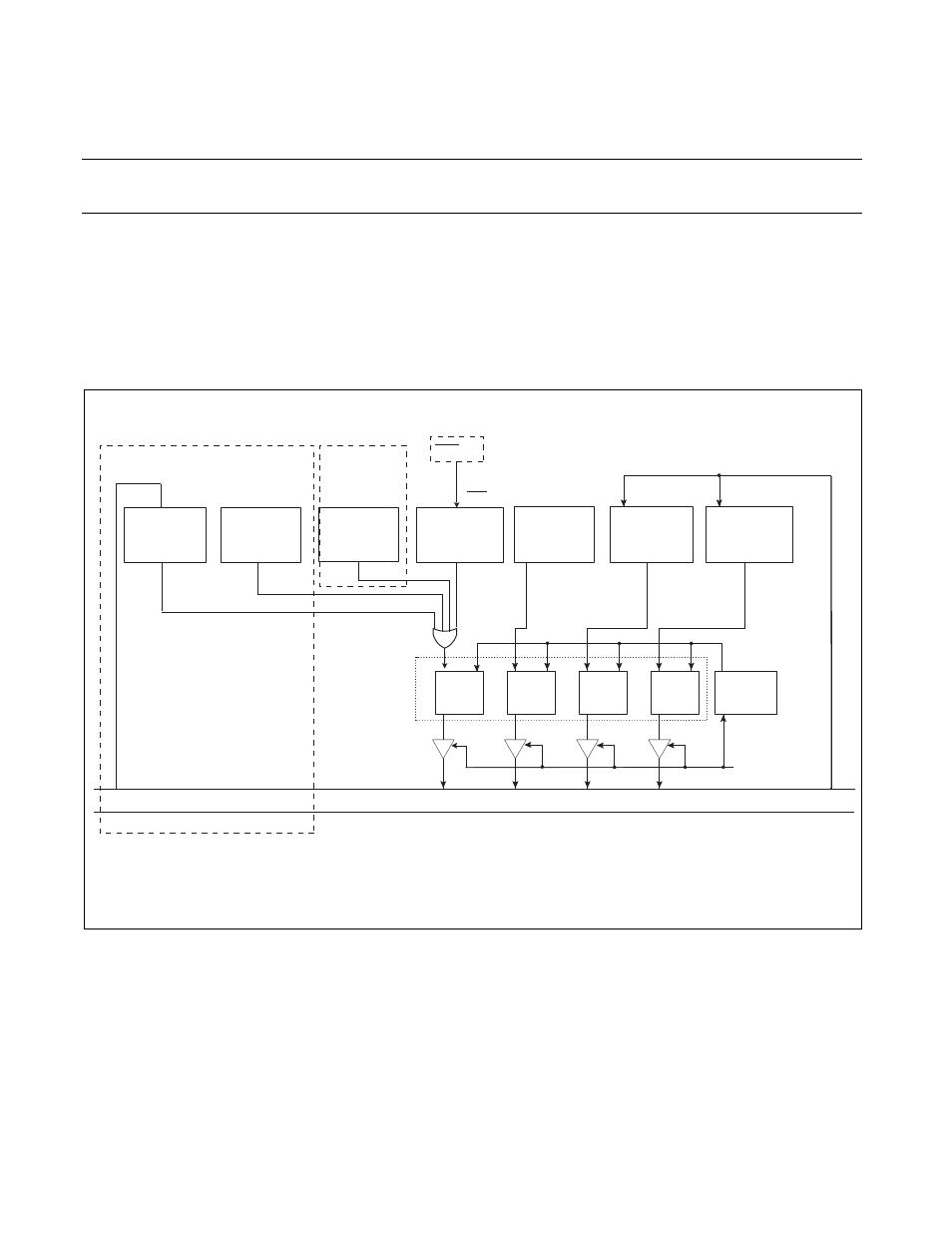

As shown in Figure 7.5-1 , a flip-flop is associated with each reset cause. The contents of the flip-flops are

obtained by reading the watchdog timer control register (WDTC). If the cause of a reset must be identified

after the reset has been cleared, the value read from the WDTC should be processed by the software and a

branch made to the appropriate program.

Figure 7.5-1 Block Diagram of Reset Cause Bits

RST=L

S

R

F/F

Q

S

R

F/F

Q

S

R

F/F

Q

S

R

F/F

Q

: Set

: Flip Flop

: Reset

: Output

For MB90F367/T(S)

MB90367/T(S)

Failure of main/

sub clock

Clock

supervisor

Watchdog timer

control register

(WDTC)

RST pin

No periodic clear

No periodic clear RST bit set

Write detection

circuit of LPMCR,

RST bits

Watchdog timer

reset generation

detection circuit

Power-on

Power-on

generation

detection circuit

External reset

request detection

circuit

Drop power

supply voltage

Low voltage

detection circuit

CPU operation

detection reset

request detetion

circuit

Clear

Delay

circuit

Read watchdog

timer control

register (WDTC)

Internal data bus

T-suffix only

S

R

Q

F/F